## **Stony Brook University**

# OFFICIAL COPY

The official electronic file of this thesis or dissertation is maintained by the University Libraries on behalf of The Graduate School at Stony Brook University.

© All Rights Reserved by Author.

## **Design of Low Noise and Low Power Front-end Readout Circuitry**

## in Radiation Detector System

A Thesis Presented

By

Yi-Shin Yeh

To

The Graduate School

in Partial Fulfillment of the

Requirements

for the Degree of

**Master of Science**

in

**Electrical Engineering**

Stony Brook University

August 2011

## STONY BROOK UNIVERSITY

## THE GRADUATE SCHOOL

## Yi-Shin Yeh

We the thesis committee for the above candidate for the Master of Science degree, hereby recommend acceptance of this thesis

Milutin Stanacevic, Advisor of Thesis

Assistant Professor, Department of Electrical and Computer Engineering

Emre Salman, Assistant Professor

Department of Electrical and Computer Engineering

This thesis is accepted by the Graduate School

Lawrence Martin

Dean of the Graduate School

#### Abstract of the Thesis

## **Design of Low Noise and Low Power Front-end Readout Circuitry**

## in Radiation Detector System

by

### Yi-Shin Yeh

#### **Master of Science**

in

## **Electrical Engineering**

Stony Brook University

#### 2011

This thesis presents a design methodology of a low-power and low-noise integrated front-end readout circuits for radiation detection. Since a charge sensitive amplifier (CSA) and a pulse shaper are essential circuit units in the low-power and low-noise front-end readout circuits, this thesis provides how to design the low power low noise CSA and the pulse shaper. The CSA can allow the electrons generated from the detector to integrate on a feedback capacitor of a CSA. The main function of a CSA is to amplify the input signal charge generated from the detector into the output voltage step signal. The input transistor optimization can significantly reduce the noise impact on the

whole system so it can help the front-end readout circuit increase the sensitivity in order to detect smaller electrons generated from the detector. The pulse shaper is a high order semi-Gaussian pulse shaping filter. The main function of the pulse shaper is to filter the output signal and noise from the CSA in order to maximize signal-to-noise ratio and obtain the lowest equivalent noise charge (ENC). In this thesis, the semi-Gaussian pulse shaper with ICON cells can achieve a longer time constant in order to minimize the noise in the circuitry.

To

My Parents and My Grandparents

For their continuous support, encouragement, and love

## TABLE OF CONTENTS

| LIS | T OF F | IGURES                                                              | viii |

|-----|--------|---------------------------------------------------------------------|------|

| LIS | T OF T | ABLES                                                               | xi   |

| AC  | KNOW   | LEDGEMENTS                                                          | xii  |

| 1.0 | Intro  | oduction                                                            | 1    |

| 1   | .1. R  | adiation Detection System Overview:                                 | 1    |

|     | 1.1.1  | Radiation Detector (Sensor):                                        | 1    |

|     | 1.1.2  | Charge Sensitive Amplifier (CSA):                                   | 2    |

|     | 1.1.3  | Pulse Shaper:                                                       | 3    |

|     | 1.1.4  | Analog-to-Digital Conversion:                                       | 4    |

| 1   | .2. O  | rganization:                                                        | 4    |

| 2.0 | The    | oretical Background                                                 | 5    |

| 2   | .1 Si  | gnal Analysis:                                                      | 5    |

| 2   | .2 N   | oise Analysis:                                                      | 6    |

|     | 2.2.1  | Noise Power Spectral Density:                                       | 6    |

|     | 2.2.2  | Thermal Noise:                                                      | 7    |

|     | 2.2.3  | Flicker Noise (1/f Noise):                                          | 8    |

|     | 2.2.4  | Shot Noise:                                                         | 8    |

|     | 2.2.5  | Noise Path:                                                         | 9    |

| 2   | .3 E   | quivalent Noise Charge (ENC):                                       | 11   |

|     | 2.3.1  | ENCws Due to Channel Thermal Noise of Input MOS Transistor:         | 11   |

|     | 2.3.2  | ENC1/f Due to 1/f Noise of Input MOS Transistor:                    | 12   |

|     | 2.3.3  | ENCwp Due to Shot Noise of the Detector leakage current:            | 12   |

| 3   | The D  | esign of the Charge Sensitive Amplifier                             | 13   |

| 3   | .1 C   | harge Sensitive Amplifier Circuit Overview                          | 13   |

| 3   | .2 A   | dvance Cascade Amplifier Design                                     | 14   |

|     | 3.2.1  | Advance Cascade Amplifier                                           | 14   |

|     | 3.2.2  | Input MOS Transistor Optimization                                   | 14   |

|     | a.     | Noise analysis in Strong Inversion Operation: (Vgs > Vth; IC > 10)  | 15   |

|     | b.     | Noise analysis in Weak Inversion Operation: (Vgs < Vth or IC < 0.1) | 17   |

|     | c.     | Noise analysis in Moderate Inversion Operation:                     | 18   |

| 3.2.3       | Gain & Bandwidth:                                                      | 20 |

|-------------|------------------------------------------------------------------------|----|

| 3.2.4       | Noise Contribution from Transistors:                                   | 21 |

| 3.2.5       | Adding a Buffer                                                        | 22 |

| 3.2.6       | Stability:                                                             | 22 |

| 3.3 Re      | set Network                                                            | 23 |

| 3.4 Co      | mpensation Circuit                                                     | 25 |

| 3.5 Tw      | o Stages of CSA                                                        | 26 |

| 3.6 Th      | e Simulation of CSA                                                    | 26 |

| 3.6.1       | AC Simulation of the Cascade Amplifier with the Buffer:                | 26 |

| 3.6.2       | Noise Simulation of the Cascade Amplifier with the Buffer:             | 28 |

| 3.6.3       | Transient Simulation of 2 Stages CSA:                                  | 28 |

| 3.6.4       | Noise Simulation of 2 Stages CSA:                                      | 30 |

| 4 The De    | sign of the Pulse Shaper                                               | 31 |

| 4.1 Sea     | ni-Gaussian Pulse Shaping Filter Overview                              | 31 |

| 4.2 Pu      | se Shaper Design Parameters                                            | 31 |

| 4.2.1       | The Order <i>n</i> of the Pulse Shaper:                                | 31 |

| 4.2.2       | Time Constant $\tau$ :                                                 | 36 |

| 4.2.3       | Design Constraints:                                                    | 40 |

| 4.3 Th      | e Design of the Semi-Gussian Pulse Shaper                              | 41 |

| 4.3.1       | The 2 <sup>nd</sup> Order Pulse Shaper with Two Real Coincident Poles: | 41 |

| 4.3.2       | The nth Order Pulse Shaper with ICON Cells:                            | 42 |

| 4.3.3       | The Third Order Pulse Shaper with ICON Cells:                          | 43 |

| 4.4 Th      | e Simulation of Pulse Shaper:                                          | 43 |

| 4.5 Th      | e Simulation of CSA and Pulse Shaper:                                  | 46 |

| 5 Conclu    | sions                                                                  | 50 |

| 6 Reference |                                                                        | 51 |

## **LIST OF FIGURES**

| Figure 1.1 Proposed Readout System Block Diagram                                              | 1  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 1.2 Sensor Model                                                                       | 2  |

| Figure 1.3 HIGH INPUT IMPEDANCE AMPLIFIER AND LOW INPUT IMPEDANCE AMPLIFIER (CSA)             | 3  |

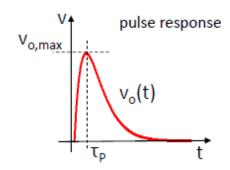

| Figure 2.1 The Pulse Response at the Output of the Pulse Shaper                               | 6  |

| Figure 2.2 Current and Voltage Noise Generators                                               | 6  |

| Figure 2.3 Linear Time-Invariant System with Transfer Function H(f)                           | 7  |

| Figure 2.4 Series Voltage and Parallel Current Thermal Noise Generators with Noiseless Device | 7  |

| Figure 2.5 Series Voltage and Parallel Current Thermal Noise Generators with MOSFET           | 8  |

| Figure 2.6 Series Voltage and Parallel Current 1/f Noise Generators with MOSFET               | 8  |

| Figure 2.7 Parallel Current Shot Noise Generator with Reverse-Biased Diode                    | 9  |

| Figure 2.8 Noise Models for Detector System                                                   | 9  |

| Figure 2.9 SIMPLIFIED NOISE RESPONSE FOR DETECTOR SYSTEM                                      | 10 |

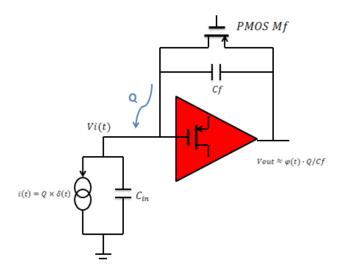

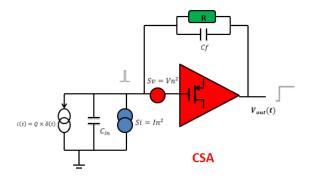

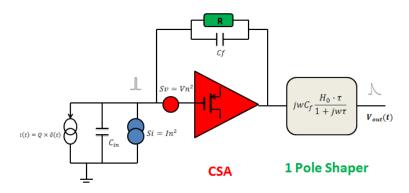

| Figure 3.1 Charge Sensitive Amplifier (with the Detector)                                     | 13 |

| Figure 3.2 Advance Cascade Amplifier                                                          | 14 |

| Figure 3.3 MOSFET Noise Model                                                                 | 15 |

| Figure 3.4 Drain-to-Source Overlap Capacitance                                                | 19 |

| Figure 3.5 Advance Cascade Amplifier                                                          | 21 |

| Figure 3.6 Advance Cascade Amplifier with white and 1/f noise generators                      | 22 |

| Figure 3.7 Adding a Source Follower, a Buffer                                                 | 22 |

| Figure 3.8 CASCADE AMPLIFIER WITH THE LOAD CAPACITANCE CL                                     | 23 |

| Figure 3.9 CSA WITH A FEEDBACK RESISTOR RF                                                    | 24 |

| Figure 3.10 CSA with a Feedback PMOS Transistor                                                           | 25 |

|-----------------------------------------------------------------------------------------------------------|----|

| Figure 3.11 CSA with a Compensation Circuit                                                               | 25 |

| Figure 3.12 Two Stages CSA                                                                                | 26 |

| Figure 3.13 The Schematic of the Advanced Cascade Amplifier                                               | 27 |

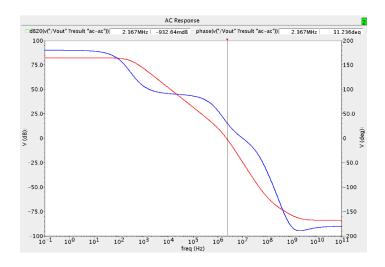

| Figure 3.14 DC Gain and Phase of the Advanced Cascade Amplifier.                                          | 28 |

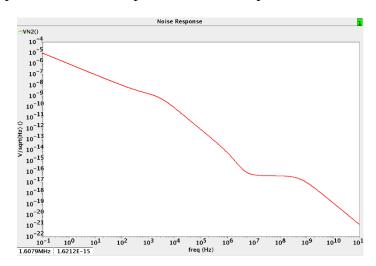

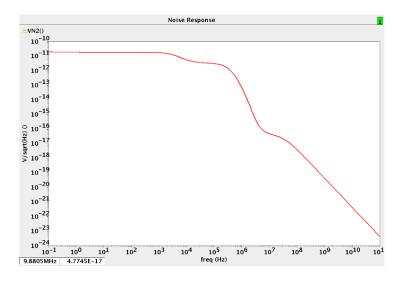

| Figure 3.15 Noise Response of the Amplifier                                                               | 28 |

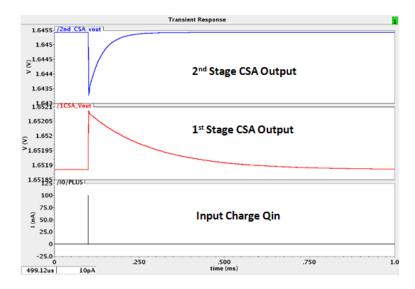

| Figure 3.16 The Schematic of 2 Stages CSA.                                                                | 29 |

| Figure 3.17 The Transient Simulation of 2 Stages CSA.                                                     | 29 |

| Figure 3.18 Noise Response of 2 Stages CSA.                                                               | 30 |

| Figure 4.1 A Typical Gaussian Shaped Signal.                                                              | 32 |

| Figure 4.2 An Unfiltered Charge Amplifier.                                                                | 32 |

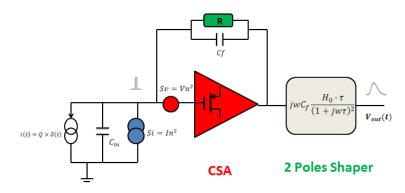

| Figure 4.3 One Real Coincident Pole Shaper with Time Constant.                                            | 33 |

| Figure 4.4 Two Real Coincident Poles Shaper with Time Constant $	au$ .                                    | 34 |

| Figure 4.5 N Real Coincident Poles Shaper with Time Constant $	au$                                        | 35 |

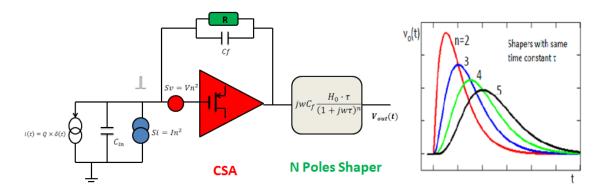

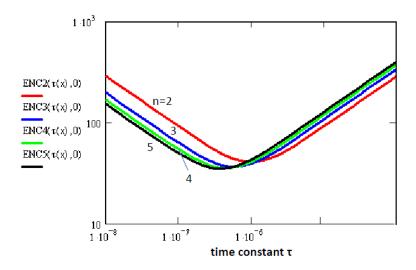

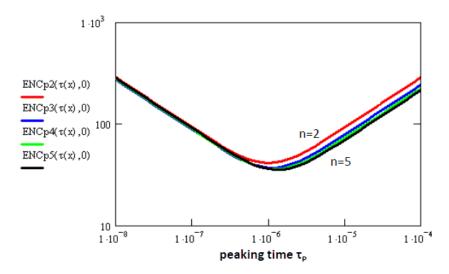

| Figure 4.6 Total <i>ENC</i> with $n$ Real Coincident Poles Shaper v.s. the Time Constant $	au$ .          | 36 |

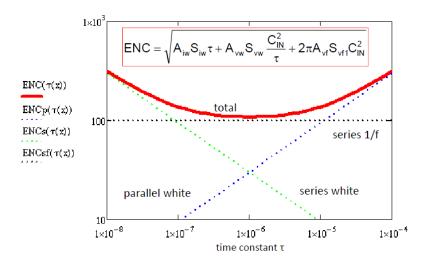

| Figure 4.7 Total <i>ENC</i> v.s. Time Constant $	au$ .                                                    | 36 |

| Figure 4.8 The $V_{out}(t)$ Pulse Response with the Peaking Time $	au_p$ .                                | 37 |

| Figure 4.9 Total <i>ENC</i> with $n$ Real Coincident Poles Shaper v.s. the Peaking Time $	au_p$           | 38 |

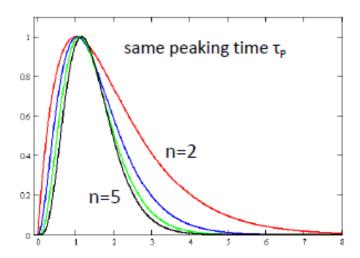

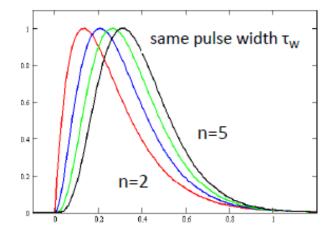

| Figure 4.10 $Vout(t)$ Pulse Response with the Same Peaking Time $	au_p$ v.s. the Order $n$ of the Shaper. |    |

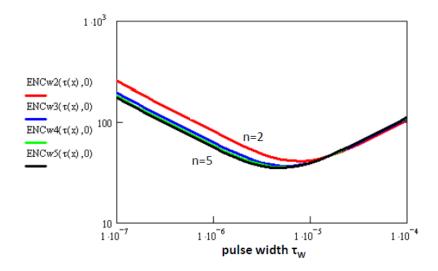

| Figure 4.11 Total <i>ENC</i> with $n$ Real Coincident Poles Shaper v.s. the Pulse Width $\tau_w$ .        | 39 |

| Figure 4.12 $Vout(t)$ Pulse Response with the Same Pulse Width $\tau_w$ v.s. the Order $n$ of the Shaper. |    |

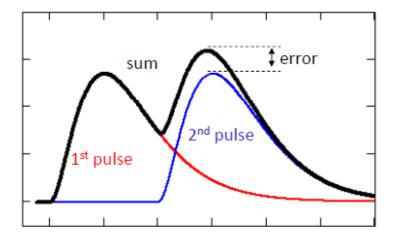

| Figure 4.13 The Pulse Pile-up.                                                                            | 41 |

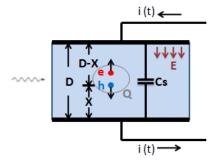

| Figure 4.14 A Sensor with Two Parallel Planar Electrodes.                                                   | 42       |

|-------------------------------------------------------------------------------------------------------------|----------|

| Figure 4.15 A 2 <sup>ND</sup> Order Pulse Shaper with Two Real Coincident Poles                             | 42       |

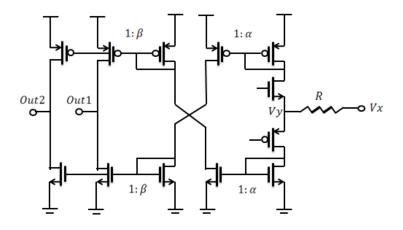

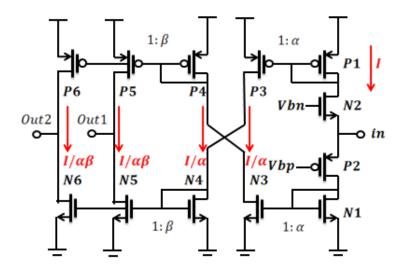

| Figure 4.16 ICON CELL.                                                                                      | 43       |

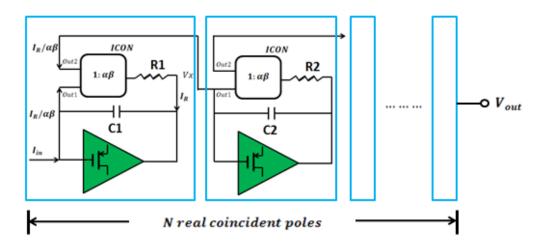

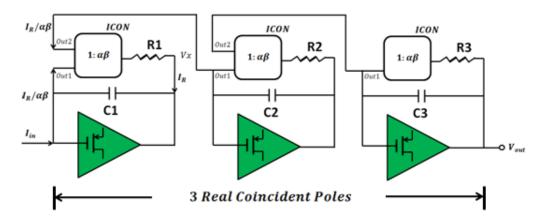

| Figure 4.17 Nth Order Shaper with ICON Cells                                                                | 43       |

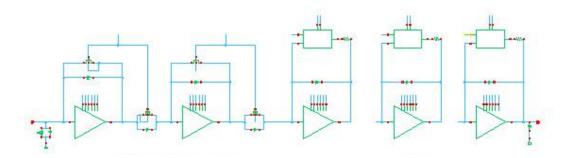

| Figure 4.18 Third Order Shaper with ICON Cells                                                              | 44       |

| Figure 4.19 The Schematic of ICON Cell                                                                      | 44       |

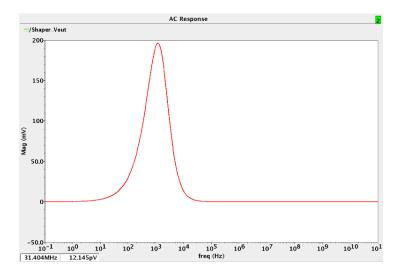

| Figure 4.20 AC RESPONSE OF THIRD ORDER PULSE SHAPER                                                         | 45       |

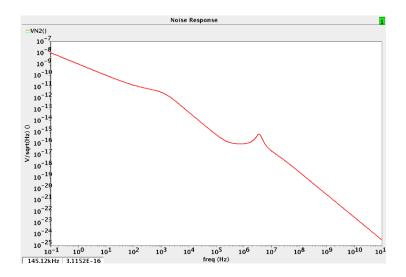

| Figure 4.21 Noise Response of Third Order Pulse Shaper                                                      | 46       |

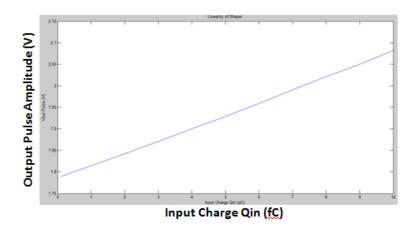

| Figure 4.22 Linearity Plot of Third Order Pulse Shaper                                                      | 46       |

| Figure 4.23 The Schematic of CSA and Pulse Shaper                                                           | 47       |

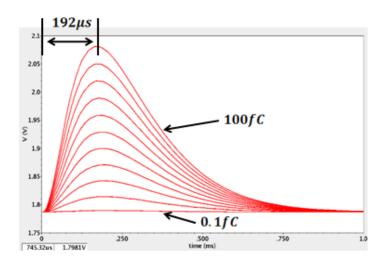

| Figure 4.24 The Shaper Output Acquired over the Entire Dynamic Range (0.1-100fC)                            | ) 47     |

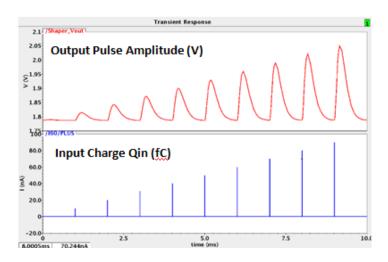

| Figure 4.25 Input Charge Qin V.S. Output Pulse Amplitude                                                    | 48       |

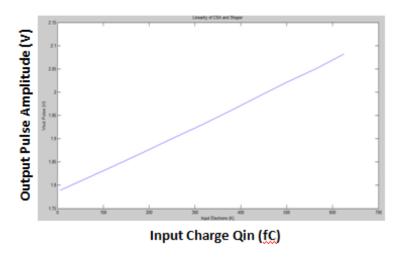

| Figure 4.26 Linearity Plot of CSA and Pulse Shaper                                                          | 48       |

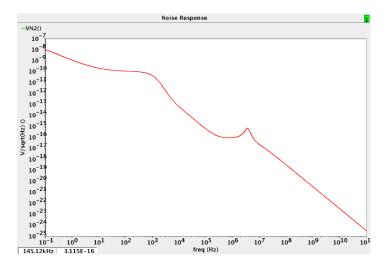

| Figure 4.27 Noise Response of CSA and the Shaper                                                            | 48       |

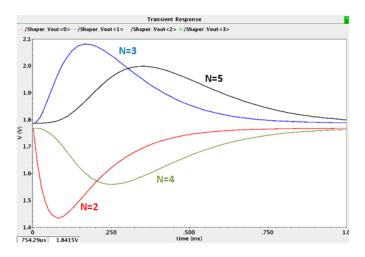

| Figure 4.28 The Output Pulse for the $2^{\text{ND}}$ to $5^{\text{TH}}$ order of Semi-Guassian Pulse Shaper | ≀ 49     |

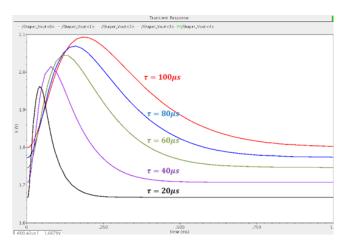

| Figure 4.29 The Output Pulse for Time Constant 20us to 100us of the 3th Order Pulseshaper.                  | SE<br>49 |

## **LIST OF TABLES**

| Table 3.1 THE SIZES OF THE TRANSISTORS, CAPACITORS, AND BIAS VOLTAGE OF THE ADVANCED               |

|----------------------------------------------------------------------------------------------------|

| CASCADE AMPLIFIER                                                                                  |

| Table 3.2 The Sizes of the Transistors, Capacitors, and Bias Voltage of the 2 Stages               |

| CSA                                                                                                |

| Table 4.1 Coefficients for $ENC$ v.s. the Order $n$ of the Shaper at Equal Time Constant $\tau$    |

|                                                                                                    |

| Table 4.2 Coefficients for $ENC$ v.s. the Order $n$ of the Shaper at Equal Peaking                 |

| Constant $\tau_p$                                                                                  |

| Table 4.3 Coefficients for $ENC$ v.s. the Order $n$ of the Shaper at Equal Pulse Width $\tau_w$ 39 |

|                                                                                                    |

| Table 4.4 The Values of Capacitors, Resistors, and Bias Voltageof the Shaper 44                    |

| Table 4.5 The Sizes of the Transistors and Bias Voltage of Each ICON Cell                          |

#### **ACKNOWLEDGEMENTS**

This thesis report would not be possible without the generous help of numerous people. First, I would like to express my deepest gratitude and appreciation to my advisor and mentor Professor Milutin Stanacevic for his guidance in this research work. He not only gave me an opportunity to work on this interesting project, but he was patient in answering all of my questions and providing g me suggestions for this research. In addition, he also offered me a lot of useful advice and insights for my life and future graduate studies.

Also, I am grateful that Professor Emre Salman took time off of his busy schedule to examine my thesis report and suggested to me some valuable advice. I would also like to extend my gratitude to Adjunct Professor Gianluigi De Geronimo for his help and instruction. His lectures and class project gave me great insight for my research. At the same time, I also appreciate Ph.D. candidate Yingkan Lin for the help he provided. My knowledge has benefited a lot from my discussions with him.

Finally, I would like to thank my parents. Without their constant support, patience, and encouragement, I would not have come to study in United States and finish my graduate studies. Their endless love and encouragement is the motivating power for me to continue my education.

## 1.0 Introduction

## 1.1. Radiation Detection System Overview:

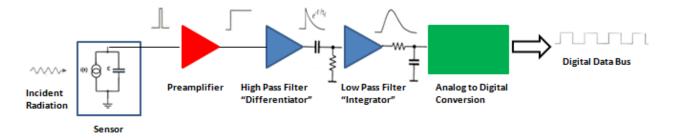

Radiation detection is one of the important applications in the design of integrated microsystems. The radiation detection system usually integrates the detectors with the electronic interface and processing circuitry. The main function of the detector, also called a sensor, is to detect high energy radiation from the physical world and convert it into an electrical signal for further signal processing. The electronic interface and processing circuitry, also called front-end readout circuitry, should be placed close to the sensor array in order to efficiently process the electrical signal from the detector. The main function of the front-end readout circuitry is to capture the weak and short electrical pulse generated by the sensors, to perform analog signal processing, and to optimize the noise from the system before analog-to-digital conversion. The digital value can represent the number of electrons produced by the detector in case of an event and should be communicated to the digital processing units. The front-end readout circuitry can be shown by a common framework as shown in Figure 1.1 and it usually contains charge sensitive amplifier (CSA), a pulse shaping filter, and analog-to-digital conversion units. Each of the circuit units is discussed below.

Figure 1.1 Proposed Readout System Block Diagram

#### 1.1.1 Radiation Detector (Sensor):

The radiation detector (the sensor) can convert the radiation energy to an electrical signal. The energy is absorbed in a semiconductor, for example silicon, which produces mobile charge carriers – electron-hole pairs. An electric field applied to the sensor sweeps the charge carriers to electrodes, inducing an electrical current. The number of electron-hole pairs is proportional to the absorbed energy, so integrating the signal current can obtain the signal charge which is also proportional to the energy. The signal charge forms a short current pulse (of order nanoseconds or less) and the spatial extent of the charge cloud is small (of order microns) [1]. The processing

circuitry can measure the amplitude and the timing of the current pulse for each event. The current pulse is coupled to a low-noise charge amplifier and sent through a pulse shaper filter.

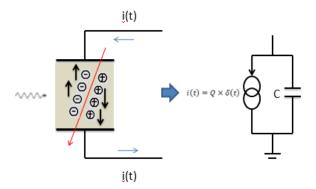

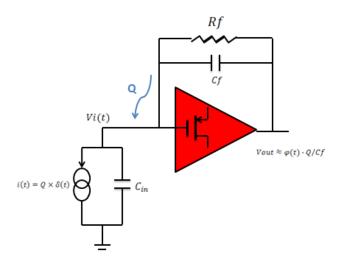

The detector can be modeled as a capacitor in parallel with a current source i(t) in Figure 1.2. The current source is represented as the electrical signal produced by the detector. The signal is a small current AC pulse, which has a time period in the nano-second range, on top of a constant DC leakage current. The constant DC leakage current is usually between 10pA to 100nA, which is dependent on the detector. The area of the AC pulse can represent the signal charge Q which is proportional to the number of electrons generated by the detector. The number of electrons is dependent on the detector and the energy of radiation source. The signal charge Q can vary from fractions of femtoCoulomb (fC) to several picoCoulomb (pC). We assume that the signal charge Q is collecting instantaneously:

$$i(t) = Q \times \delta(t)$$

, where  $\delta(t)$  is the Dirac Delta Function. (1.1)

The capacitance C as shown in Figure 1.2 represents the parasitic capacitance to the ground of the detector, and the value of the parasitic capacitance can vary from few femtoFarad (fF) to several nanoFarad (nF). For the pixel size of  $1mm^2$ , the capacitance C usually can be estimated to be 50pF. Another important design parameter is the event rate, the frequency of the AC pulse. In our design, we are dealing with the low event rate so we expect that the period of the two consecutive AC pulses is 1000ms. In order to avoid signal pile-up, the processing time of the circuitry should be kept within one tenth of the period of the two consecutive AC pulses.

Figure 1.2 Sensor Model

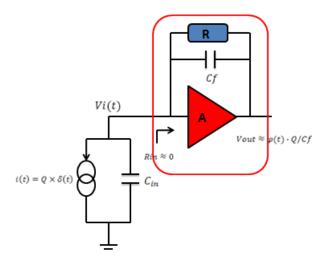

#### 1.1.2 Charge Sensitive Amplifier (CSA):

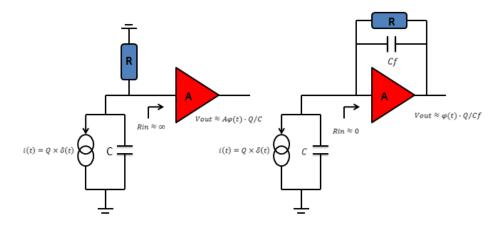

The sensor signal, the signal charge, can be quite small so the signal charge should be amplified. The signal charge from the detector can be pre-amplified in two ways: high input impedance amplifier and low input impedance amplifier as shown in Figure 1.3. In both configurations, the network R provides the discharge of C or Cf after the measurement. However, in the low-impedance configuration, the feedback network R can provide stabilization of the sensing and output nodes of the amplifier. Therefore, we prefer to use a low input

impedance amplifier by implementing a charge sensitive amplifier (CSA). With the CSA, the input charge can be integrated on a small feedback capacitance Cf and a voltage step can be obtained at the output. Therefore, the primary function of the CSA is to convert the input charge signal into the output voltage signal.

The magnitude of the sensor signal is subject to statistical fluctuations, and electronic noise further smears the signal. Therefore, the sensor and preamplifier must be designed carefully to minimize electronic noise. A critical parameter is the total capacitance in parallel with the sensor capacitance and input capacitance of the amplifier. The signal-to-noise ratio increases with decreasing capacitance. The contribution of electronic noise also relies critically on the next stage, the pulse shaper [1]-[3].

Figure 1.3 High Input Impedance Amplifier and Low Input Impedance Amplifier (CSA)

#### 1.1.3 Pulse Shaper:

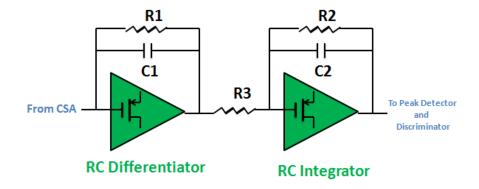

In a semiconductor detector system, the primary function of the pulse shaper is to maximize the signal-to-noise ratio. Although the signal pulses are considered as time-varying signals, the signal power is also distributed in frequency domain, derived by the pulse's Fourier transform. Since the frequency spectra of the noise and the signal is different, applying a pulse shaper after the CSA can improve the signal-to-noise ratio in order to filter the frequency response of the noise, while to tailor the frequency response to favor the signal. Since changing the frequency response also changes the time constant of the output pulse shape, that's why this function is called pulse shaping.

Figure 1.1 shows how the pulse transformation can be accomplished. The preamplifier is configured as a CSA, which converts the AC current pulse from the sensor into a step voltage signal with a long decay time. A subsequent *CR* high-pass filter (a differentiator) introduces the desired decay time and a *RC* low pass filter (an integrator) limits the bandwidth and sets the rise time. Using multiple integrators in a more complex shaper can improve the pulse symmetry. This will be discussed in more details later. When designing a pulse shaper, it is necessary to set

proper the upper frequency bound which sets the rise time, and the lower frequency bound which determines the pulse duration. In addition, finding a balance between the conflicting requirements of reducing noise and increasing speed is necessary. Sometimes the speed is important, sometimes minimum noise is paramount, but usually a compromise between the two must be found [1]-[3].

In this thesis, we choose to use a semi-Gaussian shaper in our circuitry system, since many papers [4]-[9] have proven that a semi-Gaussian shaper generally gives the best noise performance. The output of the pulse shaper is a Gaussian shaped pulse with its peak amplitude proportional to the input charge *Qin* released by the detector. The peak of the pulse is captured by the subsequent peak detector and then sent through the analog-to-digital conversion units.

#### 1.1.4 Analog-to-Digital Conversion:

The peak value of the output voltage from the pulse shaper should be sampled before it's sent to analog-to-digital converter. The peak detector can sample and capture the peak amplitude of the pulse at the output of the pulse shaper [10]-[13]. Once the peak amplitude of the pulse is sampled, it will be sent through to the analog-to-digital converter (ADC) and then we can get the digital output signals at the output of ADC for further digital signal processing.

## **1.2.** Organization:

Chapter 2 describes theoretical background about signal/noise analysis and equivalent noise charge. Chapter 3 provides the design procedures of the CSA. Chapter 4 presents the design procedures of the pulse shaper. Chapter 5 summarizes the thesis and future work.

## 2.0 Theoretical Background

## 2.1 Signal Analysis:

The input signal charge generated from the detector can be represented as a Dirac current impulse, the integral of which is equal to the charge Q corresponding to one electron charge [14]. The output signal of the CSA is an exponentially rising step function with a rise time  $\tau s$  which is inversely proportional to the gain bandwidth of the amplifier and is proportional to the detector capacitance. In fact, the rise time  $\tau s$  can be designed to be as low as possible, several nanoseconds, by increasing the gain bandwidth of the amplifier so that the output signal of the CSA can be seen approximately as an ideal step signal with an amplitude Q/Cf. The output signal of the CSA was sent through the next stage, the pulse shaper. The transfer function H(s) of the pulse shaper, a semi-Gaussian pulse shaper which consists of one RC differentiator and n RC integrators shown, is given by

$$H(s) = \left[\frac{s\tau}{1+s\tau}\right] \left[\frac{A}{1+s\tau}\right]^n \tag{2.1}$$

where  $\tau$  is the time constant of the differentiator and integrators, and A is the DC gain of the integrator. The order n of the semi-Gaussian shaper is determined by the number of real coincident poles of the shaper. In the frequency domain, the signal at the output of the pulse shaper is the product of the transfer function H(s) of the pulse shaper and the Laplace transform of the step signal Q/sCf. By taking the inverse Laplace transform of the product, the output signal in the time domain is given by

$$Vout(t) = \left(\frac{Q}{Cf}\right) \cdot h(t) = \int_{-\infty}^{+\infty} \left(\frac{Q}{sCf}\right) \cdot H(s) \cdot e^{-j2\pi f t} df = \frac{Q \cdot A^n \cdot n^n}{Cf \cdot n!} \cdot \left(\frac{t}{\tau p}\right)^n \cdot e^{-nt/\tau p}$$

(2.2)

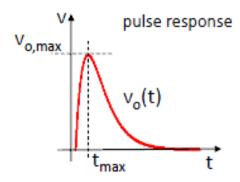

where  $\tau p$ , called peaking time of the shaper, is defined by  $\tau p = n \times \tau$ . The voltage output at the pulse shaper has a semi-Gaussian pulse shape in the time domain. The peak amplitude at the peaking time  $\tau p$  can be easily obtained by taking the derivative of equation 2.2 so that the peak amplitude at the output of the pulse shaper as shown in Figure 2.1 is given by

$$Voutmaz = \left(\frac{Q}{Cf}\right) \cdot h(t_{max}) = \frac{Q \cdot A^n \cdot n^n}{Cf \cdot n! \cdot e^n}$$

(2.3)

The peak amplitude is proportional to the charge Q generated by the detector. Therefore, the energy of radiation can be determined by measuring the peak amplitude.

Figure 2.1 The Pulse Response at the Output of the Pulse Shaper

## 2.2 Noise Analysis:

#### 2.2.1 Noise Power Spectral Density:

The power spectral density (PSD) shows how much power the signal carries at each frequency. More specifically, the PSD, Sx(f), of a noise waveform x(t) is defined as the average power carried by x(t) in an one-hertz bandwidth around f. In summary, the spectrum shows the power carried in a small bandwidth at each frequency, revealing how fast the waveform is expected to vary in the time domain [15].

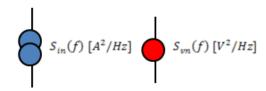

Noise generators as shown in Figure 2.2 can be represented with their power spectral density, which is the distribution of average power in the frequency domain. The variance  $\sigma_n^2$  of the noise with power spectral density Sn(f) is given by

$$\sigma_n^2 = \int_0^\infty Sn(f)df = \overline{S_n(t)^2}$$

(2.4)

Figure 2.2 Current and Voltage Noise Generators

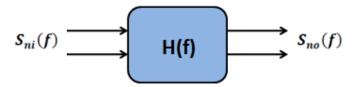

which can be applied to voltage or current noise generators. In addition, if an input referred noise with spectrum Sni(f) is applied to a linear time-invariant system with transfer function H(f) as shown in Figure 2.3, the output noise spectrum Sno(f) and the output variance  $\sigma_{no}^2$  are given by

$$\sigma_{no}^2 = \overline{S_{no}(t)^2} = \int_0^\infty S_{no}(f)df = \int_0^\infty S_{ni} \cdot |H(f)|^2 df$$

(2.5)

**Figure 2.3** Linear Time-Invariant System with Transfer Function H(f)

It agrees with our derivation that the spectrum of the signal or the noise should be shaped by the transfer function H(f).

#### 2.2.2 Thermal Noise:

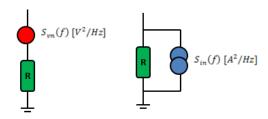

**Resistor Thermal Noise** means that the random motion of electrons in a conductor introduces fluctuations in the voltage measured across the conductor even if the average current is zero. Thus, the spectrum of thermal noise is proportional to the absolute temperature. As shown in Fig.2.4, the thermal noise of a resistor *R* can be modeled by a series voltage source or parallel current source with the one-sided spectral density

$$Sv(f) = 4KTR ; Si(f) = \frac{Sv(f)}{R^2} = \frac{4KT}{R} , f \ge 0$$

(2.6)

where  $k = 1.38 \times 10^{-23} J/K$  is the Boltzmann constant; T = 300 K is the absolute temperature; R is the resistive component of the device. Note that Sv(f) is expressed in  $V^2/Hz$ .

Figure 2.4 Series Voltage and Parallel Current Thermal Noise Generators with Noiseless Device

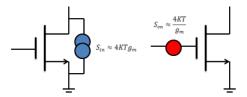

**MOSFETs** also exhibit thermal noise. The most significant source is the noise generated in the channel. It can be proven that for long-channel MOS devices operating in saturation, the channel noise can be modeled by a parallel current source connected between the drain and source terminals or by a series voltage source connected to the gate terminal as shown in Figure 2.5. Both models can be represented with their power spectral density as below.

$$Sv(f) = 4rKTgm; Si(f) = \frac{Sv(f)}{am^2} = \frac{4rKT}{am}, f \ge 0$$

(2.7)

where the coefficient r is derived to be equal to 2/3 for long-channel transistors and which may need to be replaced by a large value for submicron MOSFETs; gm is the transconductance of MOSFET [15].

Figure 2.5 Series Voltage and Parallel Current Thermal Noise Generators with MOSFET

#### 2.2.3 Flicker Noise (1/f Noise):

The interface between the gate oxide and the silicon substrate in a MOSFET entails an interesting phenomenon. Since the silicon crystal reaches an end at this interface, many dangling bonds appear, giving rise to extra energy states. As charge carriers move at the interface, some are randomly trapped and later released by such energy states, introducing flicker noise in the drain current. The flicker noise is easily modeled as a voltage source in series with the gate and roughly given by

$$Sv(f) = {}^{K}/_{Cox \cdot WL \cdot f} \tag{2.8}$$

where k is a process-dependent constant on the order of  $10^2 - 25^2(F)$ . The noise spectral density associated with dangling bonds occurs at low frequency more often. For this reason, flicker noise is also called 1/f noise, which can be modeled in Figure 2.6. The inverse dependence of 1/f noise on WL suggests that to decrease 1/f noise, the device area must be increased. Therefore, it's not surprising to see devices having areas of several thousand square microns in low-noise applications [15].

**Figure 2.6** Series Voltage and Parallel Current 1/f Noise Generators with MOSFET

#### 2.2.4 Shot Noise:

Shot noise in electronic circuits is due to the quantized nature of the electric charge. It consists of random fluctuations of the electric current in a DC current due to that current consisting of a flow of discrete electrons. The spectral noise density of shot noise is given as

$$Si(f) = 2qI (2.9)$$

where I is the average DC current, and q is the electronic charge. Note that the criterion for shot noise is that carriers are injected independently of one another, as in semiconductor diodes. The shot noise of a reverse-biased diode can be modeled by a parallel current source as shown in Figure 2.7.

Figure 2.7 Parallel Current Shot Noise Generator with Reverse-Biased Diode

#### 2.2.5 Noise Path:

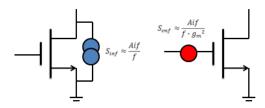

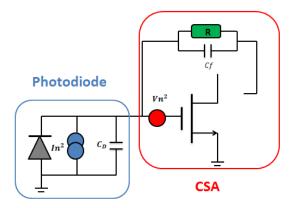

The noise properties of a front-end readout circuitry can be represented by a series voltage noise generator and a parallel current noise generator at the input of the amplifier, as shown in Figure 2.8.  $C_D$  is represented as the detector capacitance. Rather than specifying the total noise over the full bandwidth, the magnitude of each noise source generator is described by its power spectral density. According to the generally accepted assumption, the total system noise is assumed to be dominated by the leakage current of the detector and the input MOS transistor of the CSA. Since the feedback resistor R of the CSA provides a white parallel noise source at the input node of the CSA, the feedback resistor R should be very large in order to make its noise contribution negligible. Therefore, we first ignore the noise contribution from the feedback resistor R in our noise analysis. The two equivalent noise sources are given by

$$Sv = Vn^2 = \frac{8}{3} \cdot KT \cdot \frac{1}{gm} + \frac{K_f}{Cox^2 \cdot WL \cdot f}$$

(2.10)

$$Si = In^2 = 2qI \tag{2.11}$$

Figure 2.8 Noise Models for Detector System

where gm is the transconductance of the input transistor. The first term in equation 2.10 represents the channel thermal noise of the input MOS transistor. The second term in equation 2.10 represents the 1/f noise of the input MOS transistor, where Kf is the 1/f noise coefficient of the CMOS process used in [16] [17]. In addition to the input MOS transistor noise, the detector leakage current provides another noise component, which is shot noise. It generally can be expressed as equation 2.11, where I is the detector leakage current.

From the above two equations, the total noise power spectrum at the output of the CSA can be given by

$$Vn, out(s)^{2} = \left(\frac{Cf + Cgs + Cgd + C_{D}}{Cf}\right)^{2} \cdot Vn^{2} + \left(\frac{1}{sCf}\right)^{2} \cdot In^{2}$$

(2.12)

The first term in equation 2.12 represents the thermal noise and 1/f noise from the input MOS transistor and the second term is the shot noise due to the detector leakage current. The total integrated rms noise at the output of the pulse shaper must be calculated first and then we can easily calculate the signal-to-noise ratio, which is that the amplitude of the signal divided by the total integrated rms noise, at the output of the pulse shaper. The transfer function H(s) of a sem-Guassian pulse shaper consisting of one CR differentiator and n RC integrators is give by equation 2.1.

$$H(s) = \left[\frac{s\tau}{1+s\tau}\right] \left[\frac{A}{1+s\tau}\right]^n \tag{2.1}$$

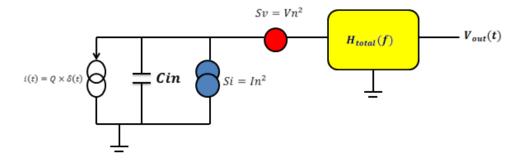

The total noise power spectrum at the output of CSA is tailored by the transfer function H(s) of the pulse shaper as shown in Figure 2.9. The total integrated rms noise at the output of the pulse shaper is then calculated as

$$\sigma_{n,tot}^{2} = Vtot^{2} = \int_{0}^{\infty} |Vo(j2\pi f)|^{2} \cdot |H(j2\pi f)|^{2} df$$

$$= \int_{0}^{\infty} Si \cdot |Htot(s)|^{2} df + \int_{0}^{\infty} Sv \cdot \omega^{2} \cdot Cin^{2} \cdot |Htot(s)|^{2} df (2.13)$$

Figure 2.9 Simplified Noise Response for Detector System

where  $Cin = Cf + Cgs + Cgd + C_D$  is equal to the sum of the capacitance; Cf is the feedback capacitance of the CSA, Cgs and Cgd is the capacitance of the input MOS transistor;  $C_D$  is the capacitance of the detector; Htot(s) is the transfer function of the whole system; Si is the equivalent parallel current noise source from the shot noise of the detector leakage current, Sv is the equivalent series voltage noise source from thermal noise and 1/f noise of the input MOS transistor.

## 2.3 Equivalent Noise Charge (ENC):

In the detector readout system, the noise performance of the system is generally expressed as the equivalent noise charge (ENC). The ENC is defined as the charge that the detector has to release in order to yield a signal-to-noise ratio to one. In order words, the ratio of the total integrated *rms* noise at the output of the pulse shaper to the signal amplitude due to one electron charge Q represents the ENC [1] [14]. ENC can be given by

$$\frac{S}{N} = \frac{Vo_{max}}{\sigma_{n,tot}} = \frac{Q \cdot h_{max}}{\sqrt{\int_0^\infty Si \cdot |Htot(s)|^2 df + \int_0^\infty Sv \cdot \omega^2 \cdot Cin^2 \cdot |Htot(s)|^2 df}}$$

$$ENC = \frac{\sqrt{\int_{0}^{\infty} Si \cdot |Htot(s)|^{2} df + \int_{0}^{\infty} Sv \cdot \omega^{2} \cdot Cin^{2} \cdot |Htot(s)|^{2} df}}{h_{max}} = \sqrt{ENC_{ws}^{2} + ENC_{1/f}^{2} + ENC_{wp}^{2}}$$

(2.14)

where ENC is commonly expressed in fC or in rms electons;  $ENC_{ws}$ ,  $ENC_{1/f}$ , and  $ENC_{wp}$  represent white series noise from the input MOS transistor, the 1/f series noise from the input MOS transistor, and the white parallel shot noise due to the detector leakage current. We try to design the front-end readout circuitry with the lowest possible ENC. Clearly, the ENC relies on the characteristics of the detector, the CSA, and the pulse shaper. Before designing the CSA and the pulse shaper, it is better to deal with each independent noise component separately.

## 2.3.1 $ENC_{ws}$ Due to Channel Thermal Noise of Input MOS Transistor:

The thermal noise source originates from the channel resistance of the input MOS transistor. Dividing the integrated rms thermal noise to the signal amplitude due to one electron charge, the  $ENC_{ws}$  is given by

$$ENC_{ws} = \frac{8}{3} \cdot KT \cdot \frac{1}{gm} \cdot \frac{(Cg + Cf + C_D)^2 \cdot B(\frac{3}{2}n - \frac{1}{2}) \cdot n}{q^2 \cdot 4\pi \cdot \tau} \cdot \left(\frac{n! \cdot e^{2n}}{n^{2n}}\right) = a_{ws} \cdot \frac{\gamma}{gm} \cdot (Cg + Cf + C_D)^2 \cdot \frac{1}{\tau} \quad (2.15)$$

where B(x, y) is the beta-function;  $a_{ws}$  is the constant shaping factor that depends on the order of the pulse shaper;  $\gamma$  is the thermal noise coefficient that depends on the operation region of transistor;  $C_D$  is the summation of the detector parasitic capacitance; Cg is the input capacitance of the input MOS transistor; Cf is the feedback capacitance of the CSA. This is a general  $ENC_{ws}$  expression and is valid for most of detector systems by using semi-Gaussian pulse shapers with

$n^{th}$  order. Obviously, the use of the pulse shaper with larger time constant  $\tau$  can limit the thermal noise. In addition, the  $ENC_{ws}$  is proportional to the input capacitance and depends slightly on the order of the pulse shaper.

## 2.3.2 $ENC_{1/f}$ Due to 1/f Noise of Input MOS Transistor:

In the design of the detector readout system, a CMOS technology process provides 1/f noise, so the detector resolution is affected by 1/f noise significantly. The 1/f noise originated from the input MOS transistor.  $ENC_{1/f}$  can be given by

$$ENC_{1/f} = \frac{\kappa_f}{cox^2 \cdot WL \cdot f} \cdot \frac{(Cg + Cf + C_D)^2}{Q^2 \cdot 2n} \cdot \left(\frac{n! \cdot e^{2n}}{n^{2n}}\right) = a_f \cdot \kappa f \cdot (Cg + Cf + C_D)^2$$

(2.16)

where  $a_f$  is the constant shaping factor that depend on the order of pulse shaper; Kf is 1/f noise coefficient of the input transistor. The equation 2.16 can show that  $ENC_{1/f}$  strongly depends on the process parameters Kf, Cox, and the input MOS transistor dimension. In addition,  $ENC_{1/f}$  is totally independent of the time constant  $\tau$  of the pulse shaper and depends slightly on the order of the pulse shaper.

## 2.3.3 $ENC_{wp}$ Due to Shot Noise of the Detector leakage current:

For the noise component 2qI, due to the detector leakage current,  $ENC_{wp}$  can be expressed as

$$ENC_{wp} = 2qI \cdot \frac{\tau \cdot B(\frac{1}{2}, n + \frac{1}{2})}{q^2 \cdot 4\pi \cdot \tau} \cdot \left(\frac{n! \cdot e^{2n}}{n^{2n}}\right) = a_{wp} \cdot I \cdot \tau \tag{2.17}$$

In contrast to  $ENC_{ws}$ ,  $ENC_{wp}$  is proportional to the time constant  $\tau$  of the pulse shaper. Furthermore, it depends on the characteristics of the shaper and is independent of the input transistor dimension.

In the following sections, we will discuss more details of *ENC* effect on the design parameters of the CSA and the pulse shaper. We want to design the lowest possible *ENC* in our front-end readout circuitry. The optimal input transistor characteristics of the CSA, the optimal peaking time of the pulse shaper, and the order of the pulse shaper will be designed in order to reach the minimum total *ENC* in our system.

## 3 The Design of the Charge Sensitive Amplifier

## 3.1 Charge Sensitive Amplifier Circuit Overview

**Figure 3.1** Charge Sensitive Amplifier (with the Detector).

Since the charge pulse released by the detector is too small to be processed, it has to be pre-amplified before any signal processing. The input pre-amplification can be performed by using a low input impedance charge sensitive amplifier (CSA). A basic structure of the CSA is shown in Figure 3.1. The CSA is composed of a voltage amplifier A, a feedback capacitor Cf, and a feedback network R. The charge Q released by the detector integrates into the feedback capacitor Cf. The main function of the CSA is to convert input current pulse into an output voltage signal [18]-[22]. If the CSA is assumed to be realized by an ideal voltage amplifier with infinite gain and bandwidth, the output of the CSA is very close to an ideal voltage step.

$$Vo(t) = \varphi(t) \cdot \frac{Q}{Cf}$$

, where  $\varphi(t) = 0$  for  $t < 0$ ; 1 for  $t > 0$ ; (3.1)

Due to the Miller effect, the input impedance of the CSA is very low so the current AC pulse mainly flows through the feedback capacitor Cf, as long as  $Cl \ll Cf \cdot A_0$ , where  $A_0$  is the small signal gain of the voltage amplifier A. The CSA provides a virtual ground at the input node so the virtual ground at the input node stabilizes the potential of the sensor electrode and the operation of the input transistor.

The CSA requires an additional feedback network R for (i) discharging the feedback capacitor Cf after each event is processed; (ii) absorbing the DC leakage current of the detector; (iii) stabilizing the bias points at input and output nodes and the operation of the voltage amplifier A by providing necessary DC feedback.

## 3.2 Advance Cascade Amplifier Design

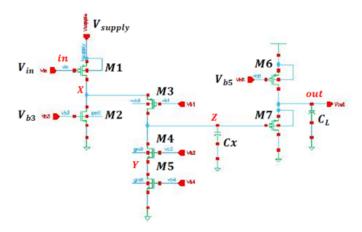

## 3.2.1 Advance Cascade Amplifier

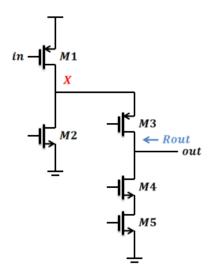

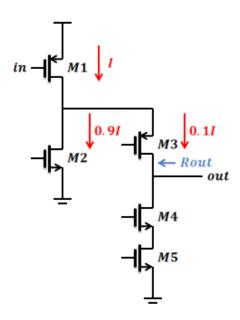

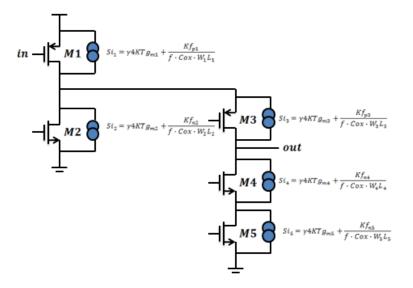

Figure 3.2 Advance Cascade Amplifier

In order to achieve a high voltage gain and wide bandwidth of the voltage amplifier, the voltage amplifier typically can be implemented by an advance cascade amplifier as shown in Figure 3.2. This configuration has several advantages. Since the cascade transistors, M3 and M4, boost the output resistance, the voltage gain of the amplifier is increased. In addition, the current of the output cascade transistors M3, M4, and M5 doesn't need to be the same as the drain current of the input transistor M1. Therefore, the input transistor M1 can operate at relatively high current to achieve high transcondunctance gm1, thus improving the voltage gain. On the other hand, the current of the output cascade transistors can be biased at relatively low current to increase the output resistance Rout, thus also increasing overall voltage gain. Usually, the current of the cascade stage is one tenth of the drain current of M1. Furthermore, using the input PMOS transistor instead of NMOS transistor provides lower 1/f noise which significantly affects the noise performance of the whole system. However, the note X adds a pole at relatively low frequency so there is a stability issue on the amplifier. It will be discussed more details later. Moreover, the output voltage range of the amplifier is also limited by the cascade configuration.

#### 3.2.2 Input MOS Transistor Optimization

In a properly designed voltage amplifier, the dominant noise sources are only from the input transistor. The other noise sources (e.g. from the cascade, load, etc.) are made negligible. We will now focus our attention on the input transistor. The parameters that directly impact the resolution of the system are input transistor capacitances and the input equivalent noise sources.

#### **MOSFET noise model:**

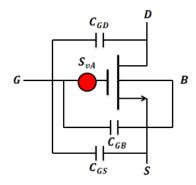

Figure 3.3 MOSFET Noise Model

Figure 3.3 shows the MOSFET noise model with series voltage noise source. Since the shot noise from the detector leakage current is only dependent on the detector and shaper characteristics instead of the design parameters of the CSA, we only should focus on the thermal noise and 1/f noise generated from the input transistor in the CSA. The series voltage noise  $S_{vA}$  of the thermal noise and of 1/f noise can be represented as

$$S_{vA} = \frac{S_{vf}}{f} + \gamma n \frac{4KT}{gm} = \frac{Kf}{Cox \cdot WL \cdot f} + \gamma n \frac{4KT}{g_{mW} \cdot W}$$

(3.2)

where n is the subthreshold slope coefficient;  $\gamma$  is the gamma coefficient from  $\frac{1}{2}$  (weak inversion) to  $\frac{2}{3}$  (strong inversion); Kf is the 1/f noise coefficient; Cox is the gate oxide capacitance per unit area; W is the width of the input transistor; L is the length of the input transistor;  $g_{mW}$  is  $g_m$  per unit W;  $i_{DW}$  is  $i_D$  per unit W; K is the Boltzman constant; and T is the absolute temperature. Then  $ENC_V$  can be expressed as

$$ENC_V^2 = \frac{A_{vw}}{\tau_p} \cdot \gamma n \cdot \frac{4KT}{gm} \cdot (Cs + Cg)^2 + 2\pi A_{vf} \cdot \frac{Kf}{cox \cdot WL} \cdot (Cs + Cg)^2$$

(3.3)

where Cs is the capacitance of the detector, and Cg is the input capacitance of the input transistor. The input transistor can operate in strong inversion, week inversion, and moderate inversion based on inversion coefficient IC. In these three different operation regions, the input transistor can have totally different noise impact on the system. Here, we discuss them separately.

## a. Noise analysis in Strong Inversion Operation: (Vgs > Vth; IC > 10)

The input transistor can work in the strong inversion if the Vgs > Vth or we can determine the work region of the transistor by the inversion coefficient  $IC = \frac{i_D}{i_S}$ .

$$i_S = 2nV_T^2 \mu Cox \frac{W}{L} \to IC = \frac{i_D}{i_S} = \frac{i_{DW} \cdot L}{2 \cdot n \cdot V_T^2 \cdot \mu \cdot Cox} > 10$$

(3.4)

where n is the subthreshold slope coefficient;  $i_{DW}$  is  $i_D$  per unit W; W is the width of the input transistor; L is the length of the input transistor;  $V_T$  is the thermal voltage;  $\mu$  is the mobility of holes in a specific process; and Cox is the gate oxide capacitance per unit area. According to the first term of equation 3.3, we know that the thermal noise is inversely proportional to the transconductance gm. In order to get gm, the drain current  $i_D$  of the input transistor at the strong inversion is given by

$$i_D = \frac{1}{2n} \cdot \mu \cdot Cox \cdot \frac{W}{L} \cdot (V_{gs} - V_{th})^2$$

(3.5)

where  $V_{th}$  is the threshold voltage; n is the subthreshold slope coefficient;  $\mu$  is the mobility of holes in a specific process; Cox is the gate oxide capacitance per unit area; W is the width of the input transistor; L is the length of the input transistor; and  $V_{gs}$  is the gate-source voltage. Then gm can be obtained by

$$gm = g_{mW} \cdot W = W \cdot \sqrt{\frac{2\mu Cox \cdot i_{DW}}{n \cdot L}}$$

(3.6)

where  $g_{mW}$  is  $g_m$  per unit W; W is the width of the input transistor; L is the length of the input transistor; n is the subthreshold slop coefficient;  $\mu$  is the mobility of holes in a specific process; Cox is gate oxide capacitance per unit area;  $i_{DW}$  is  $i_D$  per unit W. Furthermore, the input capacitance Cg of the input transistor can be expressed as

$$Cg = Cgs + Cgd + Cgb = Cox \cdot WL \tag{3.7}$$

where Cgs is the gate-source capacitance; Cgd is the gate-drain capacitance; Cgb is the gate-bulk capacitance; Cox is the gate oxide capacitance per unit area; W is the width of the input transistor; and L is the length of the input transistor. Therefore, by putting equation 3.6 and 3.7 into equation 3.2 and 3.3, the series voltage noise  $S_{vA}$  and  $ENC_V$  in strong inversion can be rewritten as

$$S_{vA} = \frac{Kf}{cox \cdot WL \cdot f} + \gamma n^{\frac{3}{2}} \cdot \frac{4KT}{W \cdot \sqrt{i_{DW}}} \cdot \sqrt{\frac{L}{2\mu Cox}}$$

(3.8)

$$ENC_V^2 = 2\pi A_{vf} \cdot \frac{\kappa_f}{\cos \kappa_W L} \cdot (Cs + \cos \kappa_W L)^2 + \frac{A_{vw}}{\tau_p} \cdot 4\kappa T \cdot \gamma \cdot n^{\frac{3}{2}} \cdot \sqrt{\frac{L}{2\mu \cos \kappa_D W}} \cdot \frac{(Cs + \cos \kappa_W L)^2}{W}$$

(3.9)

From equation 3.9, the  $ENC_V$  can be minimized by properly designing the variables of W, L,  $\tau_p$ , and  $i_{DW}$ . In order to minimize the  $ENC_V$ , the length of the input transistor can be selected as minimum length  $L_{min}$ , since the white noise term in strong inversion can be minimized. The value of  $i_{DW}$  is based on the power specification. The peaking time  $\tau_p$  is determined by the design of the pulse shaper and is based on the event rate, the charge collection time, and the parallel shot noise from the leakage current of the detector. The transistor gatewidth W has a double effect. On the one hand, increasing the gatewidth W reduces 1/f noise

due to increasing the gate area WL and also decreases the thermal noise due to increasing the  $i_{DW} \cdot W$ . On the other hand, the increase in the gatewidth W increases  $ENC_V$  due to enlarging the input capacitance Cg = CoxWL. As a result, an optimal gatewidth  $W_{opt}$  must be found for the minimum  $ENC_V$ . In our design, the noise and the power is our main concern, but there is trade-off between the power and the noise. In order to choose the proper gate size of the input transistor, we should see  $ENC_V$  in two conditions: without and within power constraints.

Without power constraint,  $i_{DW} = i_{DWmax}$  at maximum Vgs-Vth, and the length of MOSFET in strong inversion can be selected as the minimum length  $L_{min}$  in order to minimize the thermal noise of the input transistor. The equation 3.9 can be rewritten as

$$ENC_V^2 = 2\pi A_{vf} \cdot \frac{\kappa_f}{\cos w L_{min}} \cdot (Cs + \cos w L_{min})^2 + \frac{A_{vw}}{\tau_p} \cdot 4KT \cdot \gamma \cdot n^{\frac{3}{2}} \cdot \sqrt{\frac{L_{min}}{2\mu \cos i_{DWmax}}} \cdot \frac{(cs + \cos w L_{min})^2}{w} \quad (3.10)$$

For a given  $i_{DWmax}$  in equation 3.10, both the white and 1/f series noise have a minimum for = Cs (Capacitance Matching) or  $W = \frac{Cs}{C_{ox}L_{min}}$ . The minimum  $ENC_V$  in strong inversion can be given by

$$ENC_{Vmin}^{2} = 4Cs \left( \frac{A_{vw}}{\tau_{p}} \cdot 4KT \cdot \gamma \cdot n^{\frac{3}{2}} \cdot L_{min}^{\frac{3}{2}} \cdot \sqrt{\frac{Cox}{2\mu \cdot i_{DWmax}}} + 2\pi A_{vf} \cdot Kf(i_{DW}, L_{min}) \right)$$

(3.11)

With Power constraint, if we impose a limit to the dissipated power and choose  $i_D = i_{D0}$  according to our power budget, it increases the white series noise but has no impact on 1/f noise. The  $ENC_V$  can be rewritten as

$$ENC_V^2 = 2\pi A_{vf} \cdot \frac{\kappa_f}{\cos w L_{min}} \cdot (Cs + \cos w L_{min})^2 + \frac{A_{vw}}{\tau_p} \cdot 4\kappa T \cdot \gamma \cdot n^{\frac{3}{2}} \cdot \sqrt{\frac{L_{min}}{2\mu \cos v L_{Do} \cdot W}} \cdot (Cs + \cos w L_{min})^2$$

(3.12)

The 1/f series noise still has a minimum for Cg = Cs (Capacitance Matching) or  $W = \frac{Cs}{C_{ox}L_{min}}$  while the white series noise has a minimum for  $Cg = \frac{Cs}{3}$  or  $W = \frac{Cs}{3C_{ox}L_{min}}$  in strong inversion.

#### b. Noise analysis in Weak Inversion Operation: (Vgs < Vth or IC < 0.1)

For applications that have a very tight power budget, it's desirable to bias the transistor in weak inversion, Vgs < Vth. The work region of the transistor can also be determined by the inversion coefficient IC.

$$IC = \frac{i_{DW} \cdot L}{2 \cdot n \cdot V_T^2 \cdot u \cdot Cox} < 0.1 \tag{3.13}$$

where n is the subthreshold slope coefficient;  $i_{DW}$  is  $i_D$  per unit W; L is the length of the input transistor;  $V_T$  is the thermal voltage;  $\mu$  is the mobility of holes in a specific process; and Cox is the gate oxide capacitance per unit area. According to the first term of equation 3.3, we know

that the thermal noise is inversely proportional to the transconductance gm. In order to get gm, the drain current  $i_D$  of the input transistor at the strong inversion is given by

$$i_D = \mu C_{ox} V_T^2 \frac{W}{L} e^{\frac{Vgs - Vth}{nV_T}}$$

(3.14)

where  $V_{th}$  is the threshold voltage; n is the subthreshold slope coefficient;  $\mu$  is the mobility of holes in a specific process; Cox is the gate oxide capacitance per unit area; W is the width of the input transistor; L is the length of the input transistor;  $V_{gs}$  is the gate-source voltage; and  $V_T$  is the thermal voltage. Then gm can be obtained by

$$gm = g_{mW} \cdot W = W \cdot \frac{i_{DW}}{nV_T} \tag{3.15}$$

where  $g_{mW}$  is  $g_m$  per unit W; W is the width of the input transistor; n is the subthreshold slope coefficient;  $i_{DW}$  is  $i_D$  per unit W; and  $V_{th}$  is the threshold voltage. Furthermore, the input capacitance Cg of the input transistor can be expressed as

$$Cg = Cgs + Cgd + Cgb = Cox \cdot WL \tag{3.6}$$

where Cgs is the gate-source capacitance; Cgd is the gate-drain capacitance; Cgb is the gate-bulk capacitance; Cox is the gate oxide capacitance per unit area; W is the width of the input transistor; and L is the length of the input transistor. Therefore, by putting equation 3.15 and 3.6 into equation 3.2 and 3.3, the series voltage noise  $S_{vA}$  and  $ENC_V$  in weak inversion can be rewritten as

$$S_{vA} = \frac{Kf}{cox \cdot WL \cdot f} + \gamma n^2 \cdot \frac{4KT \cdot V_T}{W \cdot i_{DW}}$$

(3.16)

$$ENC_V^2 = 2\pi A_{vf} \cdot \frac{\kappa_f}{\cos w L_{min}} \cdot (Cs + \cos w L_{min})^2 + \frac{A_{vw}}{\tau_p} \cdot 4\kappa T \gamma n^2 V_T \cdot \frac{(Cs + \cos w L_{min})^2}{W \cdot l_{DW}}$$

(3.17)

**With Power constraint,** the input transistor operates in weak inversion because of the tight power budge. The 1/f noise still has a minimum for Cg = Cs (Capacitance Matching) or  $W = \frac{Cs}{C_{ox}L_{min}}$  while the white series noise has a minimum for  $W \to 0$  or  $Cg \cong 0$  in week inversion.

#### c. Noise analysis in Moderate Inversion Operation:

Most of the applications typically impose a limit of less than 1mW per pixel. With these constraints, the input MOSFET operates in a region between strong and weak inversion, known as moderate inversion. In moderate inversion the white series has a minimum for  $0 < Cg < \frac{Cs}{3}$ . Depending on the relative weight of the 1/f noise contribution, which has a minimum for Cg = Cs, the overall minimum is achieved in 0 < Cg < Cs. The optimization requires an

accurate model in the region of moderate inversion. First, the work region of the input transistor can be determined by the inversion coefficient IC.

$$0.1 < IC = \frac{i_{DW} \cdot L}{2 \cdot n \cdot V_T^2 \cdot \mu \cdot Cox} < 10$$

(3.18)

where n is the subthreshold slope coefficient;  $i_{DW}$  is  $i_D$  per unit W; L is the length of the input transistor;  $V_T$  is the thermal voltage;  $\mu$  is the mobility of holes in a specific process; and Cox is the gate oxide capacitance per unit area. According to the first term of equation 3.3, we know that the thermal noise is inversely proportional to the transconductance gm.  $g_{mW}$  is given by

$$gm = g_{mW} \cdot W = W \cdot \frac{i_{DW}}{nV_T} \cdot \frac{\sqrt{1 + 4 \cdot IC} - 1}{2 \cdot IC} = \frac{W \cdot V_T \cdot \mu Cox}{L} \cdot \left(\sqrt{1 + 4 \cdot \frac{i_{DW} \cdot L}{2 \cdot n \cdot V_T^2 \cdot \mu \cdot Cox}} - 1\right)$$

(3.19)

where  $g_{mW}$  is  $g_m$  per unit W; W is the width of the input transistor; n is the subthreshold slope coefficient;  $i_{DW}$  is  $i_D$  per unit W; L is the length of the input transistor;  $V_T$  is the thermal voltage;  $\mu$  is the mobility of holes in a specific process; and Cox is the gate oxide capacitance per unit area. In addition, Gamma coefficient  $\gamma$  also can be determined by the inversion coefficient IC [29].

$$\gamma = \begin{cases} \frac{2}{3}, IC > 10 \text{ in strong inversion} \\ \frac{1}{2}, IC < 0.1 \text{ in weak inversion} \\ r_{mod}, 0.1 < IC < 10 \text{ in moderate inversion} \end{cases}$$

(3.20)

$$r_{mod} = \frac{1}{1 + IC} \cdot \left(\frac{1}{2} + \frac{2}{3} \cdot IC\right) = \frac{1}{1 + \frac{i_{DW} \cdot L}{2 \cdot n \cdot V_T^2 \cdot \mu \cdot Cox}} \cdot \left(\frac{1}{2} + \frac{2}{3} \cdot \frac{i_{DW} \cdot L}{2 \cdot n \cdot V_T^2 \cdot \mu \cdot Cox}\right)$$

(3.21)

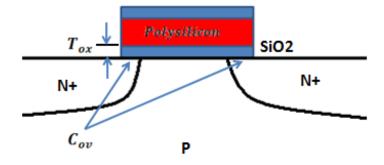

In addition, in order to get more accurate modeling, the input capacitance Cg of the input transistor can be modeled in a more advanced approach as shown in Figure 3.4.

$$Cg = C_{ox} \cdot WL \to Cg \approx 2C_{ov}W + \frac{2}{3}C_{ox}WL \tag{3.22}$$

Figure 3.4 Drain-to-Source Overlap Capacitance

where Cov is the drain-to-source overlap capacitance per unit W; Cox is the gate oxide capacitance per unit area; W is the width of the input transistor; and L is the length of the input transistor. Thus, we can put equation 3.19, 3.21, and 3.22 into equation 3.3, and then  $ENC_V$  in moderate inversion can be rewritten as

$$ENC_V^2 = \left(\frac{A_{vw}}{\tau_v} \cdot r_{mod} \cdot n \cdot \frac{4KT}{gm_{mod}} + 2\pi A_{vf} \cdot \frac{Kf}{Cox \cdot WL_{min}}\right) \cdot \left(Cs + 2C_{ov}W + \frac{2}{3}C_{ox}WL_{min}\right)^2$$

(3.23)

The equations for the optimization of the MOSFET in the moderate inversion are complex. Here, let's review the whole modeling and optimization in the moderate inversion from a more general point of view. We assume that the detector capacitance Cs is given and there is a power  $P_d$  constraint for the voltage amplifier. Imposing a constraint on power  $P_d$  means imposing a constraint on  $i_D = i_{DW} \cdot W$ , since  $i_D = P_d/Vdd$ . The constraint on the time constant  $\tau$  is dependent on the event rate, the charge collection time, and the parallel shot noise. For given constraints, since the white noise can be minimized by increasing the peaking time  $\tau_p = n \cdot \tau$ , we assume that  $ENC_V$  is dominant by 1/f noise. Thus, the 1/f series noise has a minimum for Cg = Cs (Capacitance Matching) or  $W_{opt} = \frac{Cs}{2C_{ov}W + \frac{2}{3}C_{ox}WL_{min}}$  in moderate inversion. In our design, the drain current  $i_D$  of the input transistor in the moderate inversion is designed to be 127uA and the optimum gatewidth  $W_{opt}$  is designed to be 16.8m. Since the input transistor provides a large power gain, the noise from the input transistor usually contributes more than 80% of the total voltage amplifier noise.

#### 3.2.3 Gain & Bandwidth:

In order to compromise the power and the noise, the input MOSFET can operate in a moderate region. Once we know the power constraint  $P_D$ , the drain current of the input transistor can be obtained by  $i_D = \frac{P_D}{Vdd}$ . In addition, according to the above noise analysis in moderate inversion operation, the optimum width  $W_{opt}$  of the input transistor is chosen to be  $\frac{Cs}{2C_{ov}W+\frac{2}{3}C_{ox}WL}$  due to capacitance matching, Cg = Cs. In addition, the current of the output cascade transistors M3, M4, and M5 doesn't need to be the same as the drain current of the input transistor M1. Therefore, the current of the output cascade transistors can be biased at relatively low current to increase the output resistance ro, thus also increasing overall voltage gain. Usually, the current of the cascade stage is one tenth of the drain current of M1. Therefore, according to above constraints, the transconductance  $g_{m1}$  of the input transistor has almost been fixed. If we want to enhance the amplifier gain  $A \approx g_{m1} \cdot Rout$  as shown in Figure 3.5, the only thing we can do is to increase the output resistance Rout roughly given by

$$Rout \approx [g_{m3}r_{o3}(r_{o1}||r_{o2})]|[g_{m4}r_{o4}r_{o5}]$$

(3.24)

Since  $g_{m3}r_{o3}(r_{o1}||r_{o2}) \ll g_{m4}r_{o4}r_{o5}$ , Rout is approximated by  $g_{m3}r_{o3}(r_{o1}||r_{o2})$ . Therefore, we can try to increase  $g_{m3}$  by enlarging  $W_3$  and increase  $r_{o1}, r_{o2}, r_{o3}$  by enlarging  $L_1, L_2, L_3$ . Finally, the gain A can be achieved to 80dBm. However, large  $W_1$  and  $W_3$  causes stability problem on the amplifier. We will discuss this issue later more details.

Figure 3.5 Advance Cascade Amplifier

#### 3.2.4 Noise Contribution from Transistors:

Once the input transistor noise is optimized, the noise from other transistors must be minimized as well. Since the noise calculation is complex, we use approximate equations for the noise spectral densities here. First we compute the white noise from each transistor, and then 1/f noise as shown in Figure 3.6. First of all, the noise contribution from the cascading transistors M3 and M4 is usually negligible [15]. Then, for the current source transistors M2 and M5, white noise terms can be minimized by reducing  $\gamma \cdot g_m$ . Since the higher L reduces  $\gamma \cdot g_m$ , thus lowing white noise, the length of M2 and M5 should be chosen as high as possible. For a given drain current, M2 and M5 should operate in strong inversion as well. Next we try to minimize 1/f noise by increasing both L and M of M2 and M5 while maintaining a fixed M/L ratio in order to maintain the operating point of M2 and M5. Finally, both white and 1/f noise in M2 and M5 is minimized.

**Figure 3.6**Advance Cascade Amplifier with white and 1/f noise generators

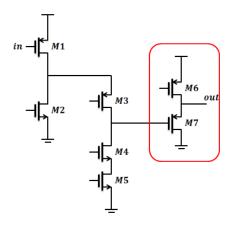

#### 3.2.5 Adding a Buffer

In Figure 3.7, a source follower is used as a buffer to drive the output and to isolate the sensitive node from the large load capacitance.

Figure 3.7 Adding a Source Follower, a Buffer

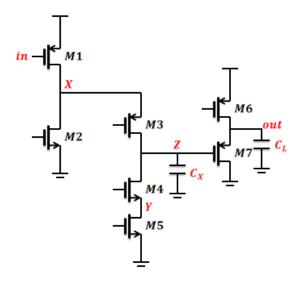

### 3.2.6 Stability:

Consider the circuit as shown in Figure 3.8. We identify five poles at the input node, the output node, node X, node Y, and node Z. In order to decrease the white noise of the load transistor  $M_5$ ,  $L_5$  is chosen as a large value and  $W_5$  is chosen as a low value. Plus, the small-signal resistance at node Y is small. Therefore, the pole at node Y locates at relatively high frequency. Furthermore, since the output resistance of the buffer is usually small, the pole at the output node also lies at relatively high frequency, even with a moderate load capacitance  $C_L$  at the output node. In addition, since the small-signal resistance at node Z is higher than the small-

signal resistance at the other nodes, even with a moderate compensate capacitance  $C_X$ , the pole at node Z is usually the dominant pole in the amplifier. Furthermore, the total capacitance at node X is roughly equal to Cgd1 + Cdb1 + Cgd2 + Cdb2 + Cgs3 + Csb3. Since W1 and W3 are usually large in our circuit in order to minimize the noise and to increase the gain, the capacitance at node X is quite large. It makes the pole at the node X be a first non-dominant pole and is close to the dominant pole at node Z, so the circuit easily becomes unstable. Thus, one way to solve unstable problem in the circuit is to increase the compensation capacitance  $C_X$  at node Z because larger compensation capacitance  $C_X$  moves the dominant pole at node Z close to the origin so that it makes the circuit more stable. However, the bandwidth becomes smaller and then the speed of the circuit is decreased. For our design, the chosen value of the compensation capacitance  $C_X$  is 2pF so the area of the compensation capacitance  $C_X$  is quite large in the circuit in order to make the circuit stable.

**Figure 3.8** Cascade Amplifier with the Load Capacitance  $\mathcal{C}_L$

## 3.3 Reset Network

The reset network R provides the discharge of the feedback capacitor after the measurement. In the low impedance configuration R also provides stabilization of the sensing node and of the voltage amplifier. The reset network can be implemented by using a very large feedback resistor Rf as shown in Figure 3.9. Since the feedback resistor Rf provides a white parallel noise source at the input node of the CSA, the feedback resistor Rf should be very large in order to make its noise contribution negligible. The relationship between the noise from the feedback resistor Rf and the noise from the detector leakage current is shown as following

$$\frac{4KT}{Rf} << 2qI_{leak} \tag{3.25}$$

where K is the Boltzman constant; T is the absolute temperature;  $i_{leak}$  is the detect leakage current; and q is the electronic charge released by the detector. However, adding a large feedback resistor Rf has several disadvantages. First, Rf is too big to integrate on the chip due to limited area. Secondly, a large Rf creates a large voltage drop between the input and output nodes of the CSA. This large voltage drop would affect the work region of the transistors and the operation of the voltage amplifier. Third, a larger Rf makes the CSA has a longer time constant due to a larger Rf value. A Longer time constant leads to a longer discharge time so that the next pulse event would easily pile-up on the previous pulse event.

**Figure 3.9** CSA with a Feedback Resistor *Rf*

An alternative is to use a single P channel MOFSFET biased in saturation as shown in Figure 3.10 [23][24]. The area of PMOS transistor is much smaller than the large feedback resistor Rf so it's easier to implement on the chip. The gate terminal of the transistor  $M_F$  is connected to a fixed biasing voltage. This biasing voltage should be chosen in order to make  $M_F$  in saturation (strong inversion) so that the PMOS transistor  $M_F$  in strong inversion has less noise contribution. The length of the transistor  $M_F$  should be selected very long,  $\frac{L}{W} \gg 1$ , so that the PMOS transistor  $M_F$  can easily operate in strong inversion by the given drain current. In addition, The PMOS transistor  $M_F$  can absorb the leakage current from the detector and provide the discharge of the feedback capacitor after the measurement. However, because of the nonlinear dependence of  $i_D$  and  $v_{gs}$  on  $M_F$ , the time dependence of the discharge of the output node doesn't show a simply exponential behavior, as in the case of the feedback resistor Rf. Therefore, a compensation circuit has to be used in order to minimize the non-linearity.

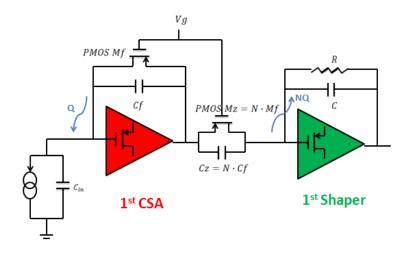

Figure 3.10 CSA with a Feedback PMOS Transistor

### 3.4 Compensation Circuit

The reset system with the compensation circuit is shown in Figure 3.11. The compensation is based on the use of a second PMOS transistor  $M_z$  in parallel to the second capacitor  $C_z$ . The source and the gate terminals of PMOS  $M_z$  are connected respectively to the source and the gate terminals of PMOS  $M_F$ . The drain terminal of PMOS  $M_z$  must be connected to the input of the pulse shaper in the next stage. In order to achieve the compensation, the length and width of PMOS  $M_z$  must respectively satisfy the conditions:  $L_z = L_F and W_z = NW_F$ , where N is the ratio of  $\frac{C_z}{C_F}$ . Therefore, the compensation circuit cancels the additional zero created by the feedback reset network. If these conditions are satisfied, the drain current of PMOS  $M_z$  is N times the drain current of PMOS  $M_F$ . And the charge  $Q_{out}$  produced by  $C_z$  is N times the charge  $Q_{in}$  generated from the detector,  $Q_{out} = N \cdot Q_{in}$ .

Figure 3.11 CSA with a Compensation Circuit

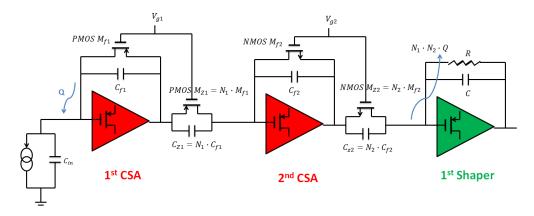

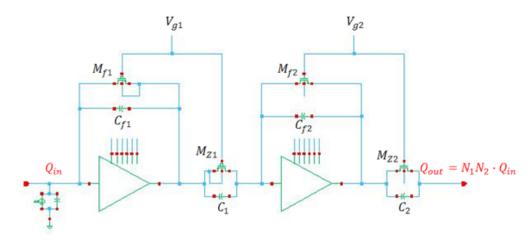

### 3.5 Two Stages of CSA

In Figure 3.12, a second CSA stage is added in order to the increase signal-to-noise ratio at the output of the pulse shaper. The compensation networks are composed by PMOS  $M_{Z1}$  parallel to  $C_{Z1}$  in the first stage and NMOS  $M_{Z2}$  parallel to  $C_{Z2}$  in the second stage. The source and the gate terminals of NMOS  $M_{Z2}$  are connected respectively to the source and the gate terminals of NMOS  $M_{f2}$ . The drain terminal of NMOS  $M_{Z2}$  must be connected to the input of the pulse shaper in the next stage. In order to achieve the compensation, the length and width of NMOS  $M_{Z2}$  must respectively satisfy the conditions:  $L_{Z2} = L_{f2}$  and  $W_{Z2} = N_2 W_{f2}$ , where  $N_2$  is the ratio of  $\frac{C_{Z2}}{C_{f2}}$ . If these conditions are satisfied, the drain current of NMOS  $M_{Z2}$  is  $N_2$  times the drain current of NMOS  $M_{f2}$ . Therefore, the drain current of NMOS  $M_{Z2}$  is  $N_1 \cdot N_2$  times the drain current of PMOS  $M_{f1}$ . And the charge  $Q_{out}$  produced by  $C_{Z2}$  is  $N_2$  times the charge  $Q_{in2}$  produced by  $C_{Z1}$ ,  $Q_{out} = N_2 \cdot Q_{in2}$ . Therefore, the overall gain is  $N_1 \cdot N_2 = \frac{Q_{out}}{Q_{in}}$ . In our design,  $N_1 = N_2 = 10$  so the overall gain is 100. The input charge released by the detector is amplified by 100 times.

Figure 3.12 Two Stages CSA

#### 3.6 The Simulation of CSA

The circuit is designed under AMI  $0.6\mu m$  CMOS technology and the supply voltage is 3.3V. This is simulated by using a Cadence Spectre simulator and BSIM3v3 transistor models.

#### 3.6.1 AC Simulation of the Cascade Amplifier with the Buffer:

Figure 3.13 below shows the schematic of the cascade amplifier. Table 3.1 lists the size of each transistor and the capacitor values in the cascade amplifier. First, the power dissipation of the CSA is limited within 1mW so the current of the input PMOS transistor should be controlled at less than  $300\mu A$ . Therefore, we controlled our input transistor current at  $127\mu A$  which is less than  $300\mu A$  so that the total power dissipation can be minimized at 0.50787mW

which is less than 1mW. Furthermore, the input PMOS transistor is chosen to operate in the moderate inversion, 0.1 < IC < 10, due to compromise the power and the noise. In the moderate inversion, the value of the input gate capacitance  $C_g$  should be chosen as less than the value of the detector parasitic capacitance  $C_S$  depending on the relative weight of 1/f series noise contribution and white series noise contribution. In our design, the optimum gatewidth size and the length size of the PMOS input transistor are chosen as 16.8m and 1.2u so that the value of the input gate capacitance  $C_g$  is about 22pF, which is less than 50pF of the detector parasitic capacitance  $C_S$ . Since the size and the current of the input PMOS transistor have been fixed, the transconductance  $g_m$  of the input PMOS transistor has also been fixed. In addition, the buffer does not provide any additional voltage gain. Therefore, in order to enhance the voltage gain of the amplifier, we can try to increase the small signal resistance ro at node Z. The small signal resistance ro at node Z can be increased by increasing  $g_{m3}$ ,  $r_{o1}$ ,  $r_{o2}$ , and  $r_{o3}$ . Finally, the gain of the amplifier can reach  $82.28 \ dBm$  as shown in Figure 3.16.

Figure 3.14 also shows the phase of the amplifier. Since the first non-dominant at node X is close to the dominant pole at node Z, it easily makes the amplifier unstable so we add a compensation capacitor  $C_X$  at node Z in order to stabilize the amplifier. The value of the compensation capacitor  $C_X$  is chosen as 2pF so that the phase margin can be achieved to  $31.236^{\circ}$ .

Figure 3.13 The Schematic of the Advanced Cascade Amplifier

| W/L PMOS M1 | $16.8  m  /  1.2  \mu$ | $V_{supply}$ | 2.5 V       |

|-------------|------------------------|--------------|-------------|

| W/L NMOS M2 | 90 μ / 21 μ            | $V_{in}$     | 1.65 V      |

| W/L PMOS M3 | 130 μ / 1.2 μ          | $V_{b1}$     | 1.2 V       |

| W/L NMOS M4 | 90 μ / 0.6 μ           | $V_{b2}$     | 1 V         |

| W/L NMOS M5 | $30\mu$ / $12\mu$      | $V_{b3}$     | 1.4 V       |

| W/L PMOS M6 | 24 μ / 2.4 μ           | $V_{b4}$     | 0.9 V       |

| W/L PMOS M7 | 60 μ / 0.6 μ           | $V_{b5}$     | 2 V         |

| $C_X$       | 2 pF                   | $C_L$        | 1 <i>pF</i> |

**Table 3.1** The Sizes of the Transistors, Capacitors, and Bias Voltage

Figure 3.14 DC Gain and Phase of the Advanced Cascade Amplifier

#### 3.6.2 Noise Simulation of the Cascade Amplifier with the Buffer:

Once the size of the input PMOS transistor is optimized, other transistors in the amplifier also need to be given proper values in order to minimize the noise. Figure 3.15 shows the noise simulation of the amplifier. The total output noise of the amplifier is calculated at  $7.58215\mu V^2$ .

Figure 3.15 Noise Response of the Amplifier

#### 3.6.3 Transient Simulation of 2 Stage CSA:

Figure 3.16 below shows the schematic of the 2 stages of the CSA. Table 3.2 lists the sizes of transistors, the values of capacitors, and the bias voltage in the 2 stage CSA. Adding one more stage of the CSA can improve the signal-to-noise ratio at the output of the pulse shaper. In addition, the compensation networks, composed of PMOS  $M_{Z1}$  parallel to  $C_1$  in the first stage and NMOS  $M_{Z2}$  parallel to  $C_2$  in the second stage, are used to improve the linearity problem

caused by the feedback transistors PMOS  $M_{f1}$  and NMOS  $M_{f2}$ . Moreover, the drain current of NMOS  $M_{Z2}$  is 100 times the drain current of PMOS  $M_{f1}$  and the output charge  $Q_{out}$  is 100 times the input charge  $Q_{in}$  generated by the detector. Therefore, the overall gain is  $N_1 \cdot N_2 = 100$ . Figure 3.17 shows the transient simulation of the 2 stages of the CSA by giving 625K input electrons which is about a 100fC input charge.

Figure 3.16 The Schematic of 2 Stages CSA

| W/L PMOS $M_{f1}$  | 1.5 μ / 30 μ | W/L NMOS $M_{f2}$     | $1.8\mu$ / $60\mu$  |

|--------------------|--------------|-----------------------|---------------------|

| W/L PMOS $M_{Z1}$  | 15 μ / 30 μ  | W/L NMOS $M_{Z2}$     | $18 \mu$ / $60 \mu$ |

| $\mathcal{C}_{f1}$ | 1 <i>pF</i>  | $\mathcal{C}_{\!f^2}$ | 1 <i>pF</i>         |

| $\mathcal{C}_1$    | 10 <i>pF</i> | $\mathcal{C}_2$       | 10 <i>pF</i>        |

| $V_{g1}$           | 0.8 V        | $V_{g2}$              | 3.1 V               |

| $N_1 = C_{f1}/C_1$ | 10           | $N_2 = C_{f2}/C_2$    | 10                  |

**Table 3.2** The Sizes of the Transistors, Capacitors, and Bias Voltage

Figure 3.17 The Transient Simulation of 2 Stages CSA

#### 3.6.4 Noise Simulation of 2 Stage CSA:

Figure 3.18 shows the noise response of the 2 stages of the CSA. The noise contribution from PMOS  $M_{Z1}$  and NMOS  $M_{Z2}$  in the compensation networks is negligible. Since the feedback transistor PMOS  $M_{f1}$  in the first stage and the feedback transistor NMOS  $M_{f2}$  in the second stage are biased at the strong inversion, the noise contribution from  $M_{f1}$  and  $M_{f2}$  can be minimized. Even though the feedback transistors  $M_{f1}$  and  $M_{f2}$  contribute some noise, the total output noise contribution from the input transistor of the amplifier is still dominant in the CSA. Therefore, the total output noise of the 2 stage CSA is calculated at  $1.209393\mu V^2$  integrated from 0.1 to  $100 \, \text{GHz}$ .

Figure 3.18 Noise Response of 2 Stages CSA

# 4 The Design of the Pulse Shaper

### 4.1 Semi-Gaussian Pulse Shaping Filter Overview

The primary function of the pulse shaper is to shape the output signal from the preamplifier in order to optimize the signal-to-noise ratio at the output of the shaper. In addition, the pulse shaper should operate properly at a high counting rate without degrading resolution. The most common pulse shaper employed in the radiation detector system is the semi-Gaussian pulse shaper achieved by one CR differentiator and n RC integrators [4]-[9]. A differentiator, a high-pass filter, sets the duration of the pulse by introducing a decay time constant  $\tau$ , and an integrator, a low-pass filter, increases the rise time to limit the noise bandwidth. The transfer function of a semi-Gaussian pulse shaper is given by

$$H(s) = \left[\frac{s\tau}{1+s\tau}\right] \left[\frac{A}{1+s\tau}\right]^n \tag{4.1}$$