# **Stony Brook University**

# OFFICIAL COPY

The official electronic file of this thesis or dissertation is maintained by the University Libraries on behalf of The Graduate School at Stony Brook University.

© All Rights Reserved by Author.

# Energy-Efficient Local Storage Design With Superconductor Reciprocal Quantum Logic

A Dissertation Presented

by

### **Zuoting Chen**

$\operatorname{to}$

The Graduate School

in Partial Fulfillment of the Requirements

for the Degree of

### Doctor of Philosophy

in

### **Computer Engineering**

Stony Brook University

December 2015

Copyright by Zuoting Chen 2015

#### Stony Brook University

The Graduate School

#### **Zuoting Chen**

We, the dissertation committee for the above candidate for the Doctor of Philosophy degree, hereby recommend acceptance of this dissertation.

Mikhail Dorojevets – Dissertation Advisor Associate Professor, Department of Electrical and Computer Engineering

Sangjin Hong – Chairperson of Defense Professor, Department of Electrical and Computer Engineering

Emre Salman Assistant Professor, Department of Electrical and Computer Engineering

> Jennifer L. Wong Assistant Professor, Department of Computer Science Stony Brook University

> This dissertation is accepted by the Graduate School.

#### Charles Taber Dean of the Graduate School

# Energy-Efficient Local Storage Design With Superconductor Reciprocal Quantum Logic

by

Zuoting Chen

#### Doctor of Philosophy

in

#### **Computer Engineering**

Stony Brook University

#### 2015

Superconductor single flux quantum (SFQ) technology is one of the promising candidates for energy-efficient high-performance computing. A new generation of SFQ logics, Reciprocal Quantum Logic (RQL) with no static power dissipation in bias resistors, offers an opportunity to dramatically decrease energy consumption in superconductor processors. Although several low complexity RQL processing units have already been demonstrated, the use of RQL for local storage design has not been explored yet.

The objective of this dissertation is to design on-chip local storage structures such as memory, register files, and caches with RQL technology and analyze their energy efficiency, complexity, and performance characteristics. The physical chip design of these RQL storage units is not feasible at this point because both CAD tools for physical VLSI chip design and as well as a target fabrication process are under development at Northrop-Grumman Systems Corp. (Baltimore, MD) and MIT Lincoln Laboratory, respectively. In order to achieve our goal, the layout-aware cell-level design process using VHDL RQL cell library developed at the Ultra High Speed Computing Lab in Stony Brook University has been used. The SBU VHDL RQL cell library specifies the dynamic and standby energy consumption, latency, JJ complexity, and approximate sizes of individual cells based on the input received from the JJlevel RQL designers. Clock propagation skew and wire delays are accounted for during circuit simulation. The circuit simulation is done with Mentor Graphics design and verification tools. As a result of the work, key characteristics of the 8.5 GHz multiported RQL storage structures with their capacity in the range of 1-4 kbit have been determined. The average energy consumption of the RQL storage designs is ~3.0-9.5 fJ/bit/operation at room temperature and the cryo-cooling efficiency is 0.1%.

The data from this dissertation also reveal the critical issues that need to be considered in the RQL storage design. These will be helpful for further development on superconductor VLSI design.

# Contents

| Abstr                                                                                                 | act                                                                                                                                                                                                                                                                                                                                                                                 | iii                                                       |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Conte                                                                                                 | nts                                                                                                                                                                                                                                                                                                                                                                                 | $\mathbf{v}$                                              |

| List o                                                                                                | f Figures                                                                                                                                                                                                                                                                                                                                                                           | viii                                                      |

| List o                                                                                                | f Tables                                                                                                                                                                                                                                                                                                                                                                            | xi                                                        |

| Ackno                                                                                                 | owledgments                                                                                                                                                                                                                                                                                                                                                                         | xii                                                       |

| Vita                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                     | xiv                                                       |

| Publi                                                                                                 | cations                                                                                                                                                                                                                                                                                                                                                                             | $\mathbf{x}\mathbf{v}$                                    |

| <ol> <li>Fu:</li> <li>1.1</li> <li>1.2</li> <li>1.3</li> <li>1.4</li> <li>1.5</li> <li>1.6</li> </ol> | adamentals of Superconductor TechnologyIntroductionJosephson JunctionsRapid Single Flux Quantum LogicEnergy-Efficient RFSQ LogicBrief Introduction to Other Superconductor Logic FamiliesPrior Work on SFQ Logic1.6.1100 GHz SFQ Bit-Serial Adder1.6.2Fujitsu's 8-bit DSP Microprocessor1.6.3FLUX-1 Microprocessor1.6.4CORE1 Microprocessor1.6.520 GHz 8-bit RSFQ Frontier Datapath | 1<br>2<br>4<br>8<br>9<br>10<br>10<br>10<br>11<br>13<br>14 |

| 2 Re<br>2.1<br>2.2<br>2.3<br>2.4                                                                      | ciprocal Quantum Logic<br>Overview                                                                                                                                                                                                                                                                                                                                                  | <b>15</b><br>15<br>17<br>18<br>20                         |

|          |     | 2.4.1 Passive Transmission Line Receiver                                                                         |

|----------|-----|------------------------------------------------------------------------------------------------------------------|

|          |     | 2.4.2 AndOr Gate                                                                                                 |

|          |     | 2.4.3 AnotB Gate                                                                                                 |

|          |     | $2.4.4  \text{Set/Reset Gate}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                  |

|          |     | 2.4.5 Non-Destructive Read-out Single-Bit Storage Cell 23                                                        |

|          | 2.5 | Fabricated RQL Design                                                                                            |

|          | 2.6 | SBU RQL VHDL Cell Library                                                                                        |

|          |     | 2.6.1 Clock Model                                                                                                |

|          |     | 2.6.2 Data Signal Model                                                                                          |

|          |     | 2.6.3 Acknowledgements                                                                                           |

|          | 2.7 | Target Fabrication Technology    22                                                                              |

| 3        | Sup | perconducting Memory and Research Goals 33                                                                       |

|          | 3.1 | Brief Review of Superconducting Memory 33                                                                        |

|          |     | 3.1.1 Wholly SFQ memory $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 32$                             |

|          |     | 3.1.2 Hybrid Josephson-CMOS Memory                                                                               |

|          |     | 3.1.3 JJ-MRAM                                                                                                    |

|          | 3.2 | New Opportunities in Energy-Efficient Local Storage Units De-                                                    |

|          |     | sign with RQL                                                                                                    |

|          | 3.3 | Research Goals                                                                                                   |

| <b>4</b> | Loc | al RAM with 1 Read and 1 Write Ports 30                                                                          |

|          | 4.1 | Design Overview                                                                                                  |

|          | 4.2 | RQL RAM Design                                                                                                   |

|          |     | 4.2.1 Decoder                                                                                                    |

|          |     | $4.2.2  \text{Data Slice}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                      |

|          |     | 4.2.3 Memory Macrocell                                                                                           |

|          |     | 4.2.4 Pipeline Structure                                                                                         |

|          |     | 4.2.5 Critical Path                                                                                              |

|          | 4.3 | Simulation Results and Discussion                                                                                |

|          |     | 4.3.1 Latency                                                                                                    |

|          |     | $4.3.2  \text{Design Complexity}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $               |

|          |     | 4.3.3 Energy Consumption                                                                                         |

| <b>5</b> | Reg | gister Files with 2 Read and 1 Write Ports 54                                                                    |

|          | 5.1 | Design Overview $\ldots \ldots 54$  |

|          | 5.2 | RQL Register File Design 54                                                                                      |

|          |     | 5.2.1 Data Slice $\ldots \ldots 5'$ |

|          |     | 5.2.2 Register Macrocell                                                                                         |

|          |     | 5.2.2 Register Macrocell                                                                                         |

|          | 5.3 | Simulation Results and Discussion                                                                                |

|          |              | 5.3.2Design Complexity65.3.3Energy Consumption6                                                                                             |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 6        | 117          |                                                                                                                                             |

| 0        |              | te-through and Write-back Caches       7         Design Overview       7                                                                    |

|          | $6.1 \\ 6.2$ | 8                                                                                                                                           |

|          | 0.2          | •                                                                                                                                           |

|          |              |                                                                                                                                             |

|          |              | 6.2.2       Directory       74         6.2.3       Write Buffer       76                                                                    |

|          |              | 6.2.4         Data Block         70                                                                                                         |

|          |              |                                                                                                                                             |

|          |              | 8                                                                                                                                           |

|          | 69           | 1                                                                                                                                           |

|          | 6.3          |                                                                                                                                             |

|          |              | J.                                                                                                                                          |

|          |              |                                                                                                                                             |

|          |              | 6.3.3 Energy Consumption                                                                                                                    |

| <b>7</b> | Firs         | t-In First-Out Buffers 85                                                                                                                   |

|          | 7.1          | Design Overview                                                                                                                             |

|          | 7.2          | RQL FIFO Buffer Design    80                                                                                                                |

|          |              | 7.2.1 Control Circuit                                                                                                                       |

|          |              | 7.2.2 Memory Array                                                                                                                          |

|          |              | 7.2.3 Pipeline                                                                                                                              |

|          | 7.3          | Simulation Results and Discussion                                                                                                           |

|          |              | 7.3.1 Latency                                                                                                                               |

|          |              | 7.3.2 Design Complexity $\dots \dots \dots$ |

|          |              | 7.3.3 Energy Consumption                                                                                                                    |

| 8        | Sun          | nmary 90                                                                                                                                    |

|          | 8.1          | Completed Work and Discussion                                                                                                               |

|          | 8.2          | Future Work                                                                                                                                 |

|          |              |                                                                                                                                             |

# List of Figures

| 1.1  | Josephson junction structure and circuit symbol                                                          | 3 |

|------|----------------------------------------------------------------------------------------------------------|---|

| 1.2  | I-V characteristics of Josephson junction.                                                               | 4 |

| 1.3  | Superconductor ring and SFQ pulse                                                                        | 5 |

| 1.4  | JTL and PTL connections used in superconductor logic                                                     | 6 |

| 1.5  | RSFQ D flip-flop                                                                                         | 7 |

| 1.6  | Biasing in RSFQ and ERSFQ circuits                                                                       | 9 |

| 1.7  | 100 GHz bit-serial adder                                                                                 | ) |

| 1.8  | Microphotograph of Fujitsu's 8-bit DSP based on latching logic. 11                                       | 1 |

| 1.9  | The FLUX-1 8-bit RSFQ microprocessor                                                                     | 2 |

| 1.10 | Microphotograph of CORE1 $\gamma$ 8 × 8 mm <sup>2</sup> chip                                             | 4 |

| 2.1  | RQL schematic                                                                                            | 7 |

| 2.2  | Data in RQL                                                                                              | 7 |

| 2.3  | RQL connection cell                                                                                      | 3 |

| 2.4  | Four-phase clocking                                                                                      | 9 |

| 2.5  | Several RQL cells in a same phase                                                                        | ) |

| 2.6  | Receiver and passive transmission line                                                                   | ) |

| 2.7  | AndOr gate                                                                                               | 1 |

| 2.8  | AnotB gate                                                                                               | 2 |

| 2.9  | Set/Reset gate. $\ldots \ldots 23$ | 3 |

| 2.10 | Non-destructive read-out storage cell schematic                                                          | 4 |

|      | 8-bit Kogge-Stone CLA                                                                                    | õ |

| 2.12 | Clock signal in VHDL model                                                                               | 7 |

|      | Data signal in VHDL model                                                                                | 3 |

|      | MIT LL SFQ process                                                                                       | ) |

| 2.15 | Cross section of the SFQ5ee process                                                                      | ) |

| 3.1  | Hybrid Josephson-CMOS RAM                                                                                | 3 |

| 3.2  | The performance gap between processor and memory $34$                                                    | 4 |

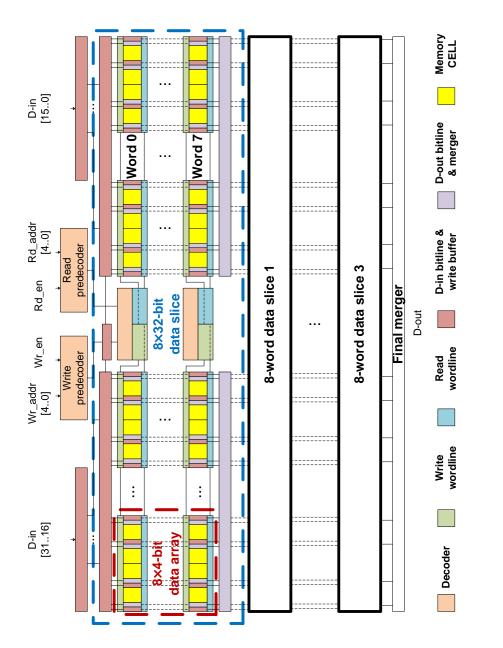

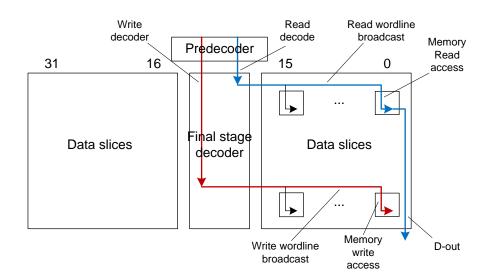

| 4.1  | Top-level structure of a 1 Kbit memory                                                                   | 3 |

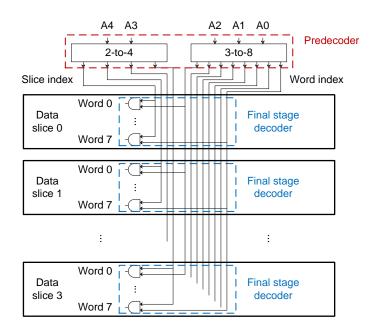

| 4.2  | A 1 Kbit RAM decoder schematic                                                                           | 9 |

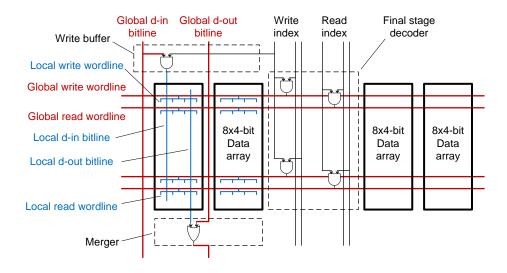

| 4.3  | Memory data slice                                              |

|------|----------------------------------------------------------------|

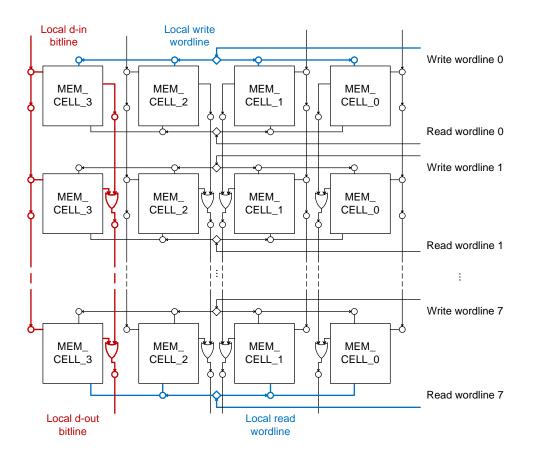

| 4.4  | Memory data array                                              |

| 4.5  | Memory macrocell                                               |

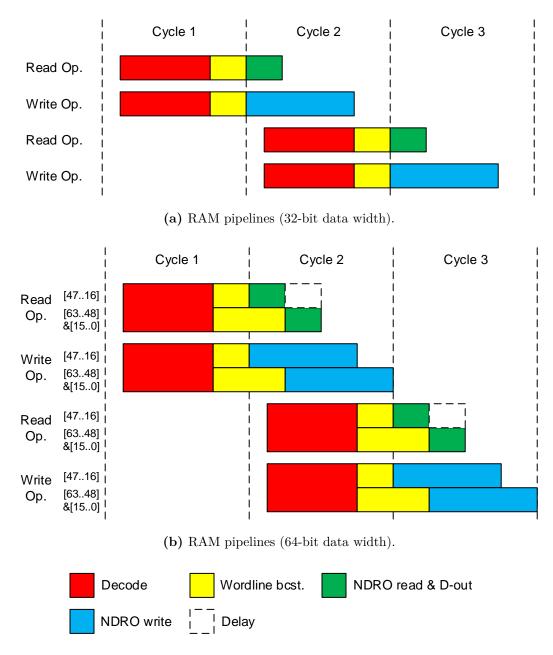

| 4.6  | RAMpipelines                                                   |

| 4.7  | Critical path in a RAM                                         |

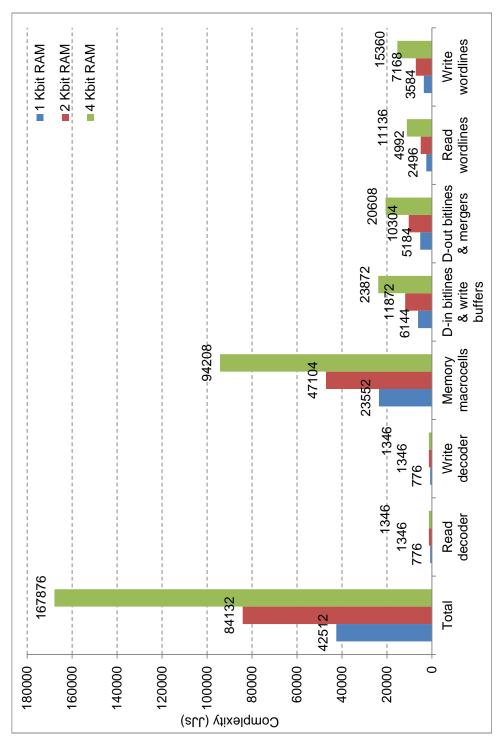

| 4.8  | RAM complexity breakdown                                       |

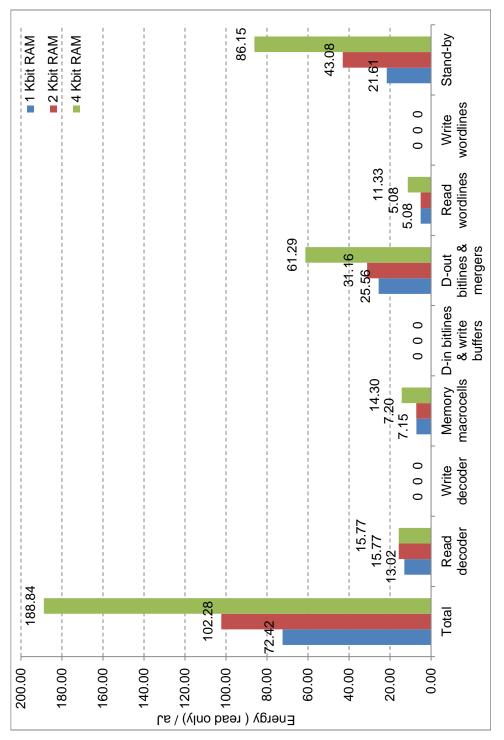

| 4.9  | RAM energy per read only operation                             |

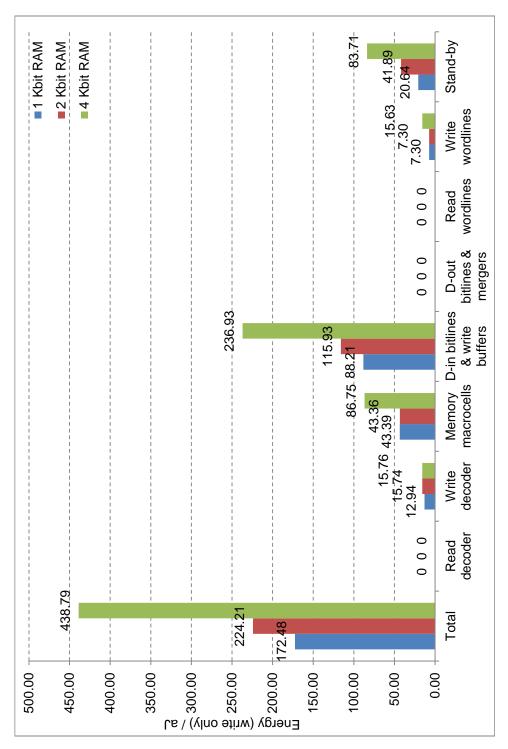

| 4.10 | RAM energy per write only operation                            |

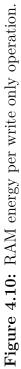

| 4.11 | RAM energy per read $+$ write operation                        |

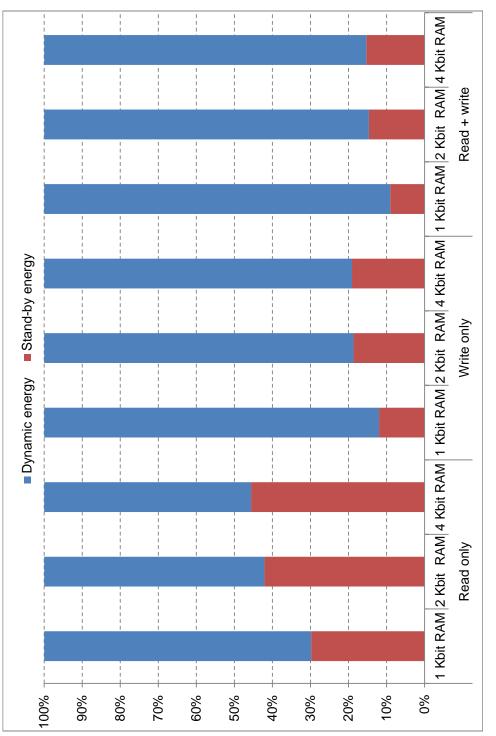

| 4.12 | RAM dynamic and stand-by energy breakdown                      |

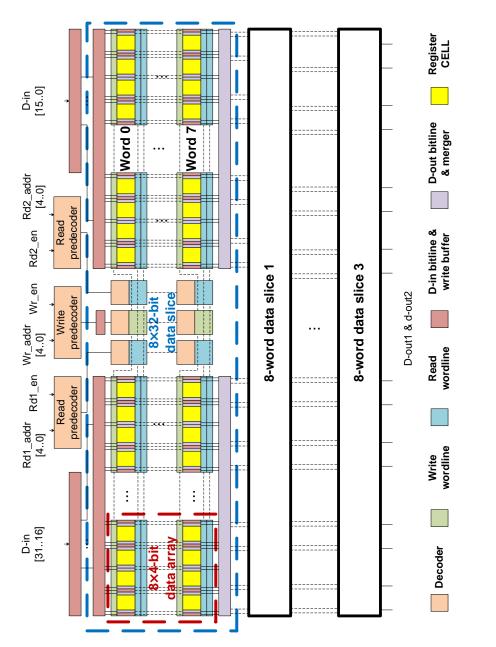

| 5.1  | Top-level structure of a 1 Kbit register file                  |

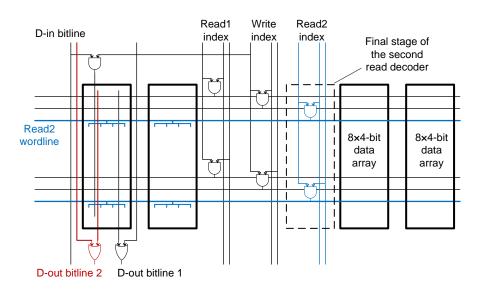

| 5.2  | Register file data block                                       |

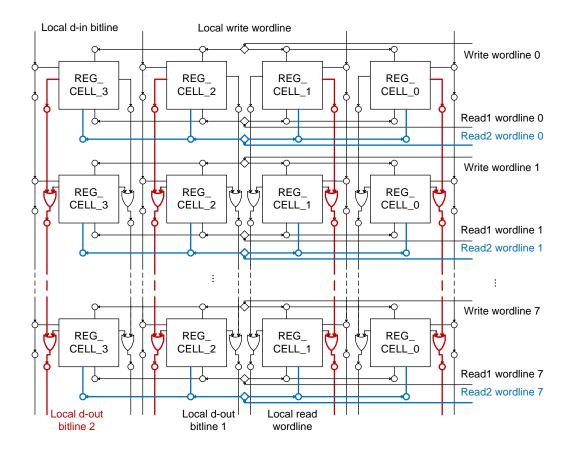

| 5.3  | Register file data array                                       |

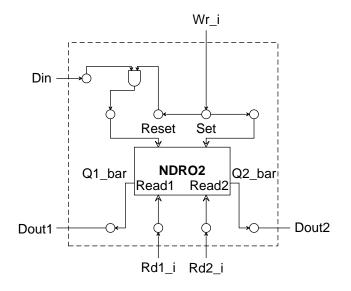

| 5.4  | NDRO2 schematic                                                |

| 5.5  | Register macrocell                                             |

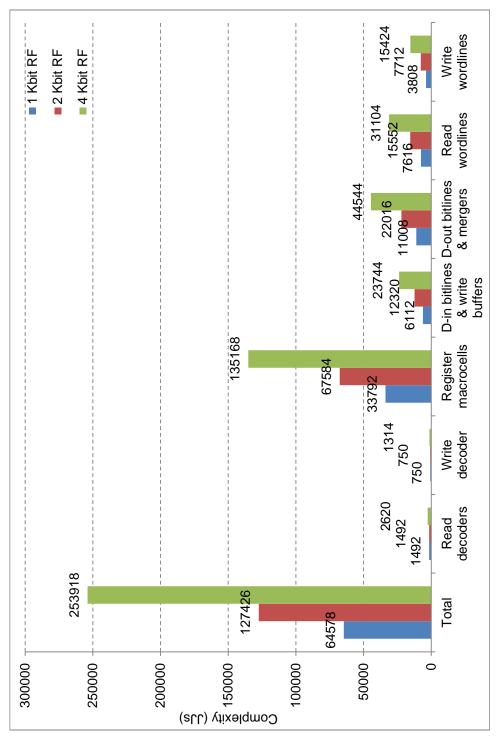

| 5.6  | Register file complexity breakdown                             |

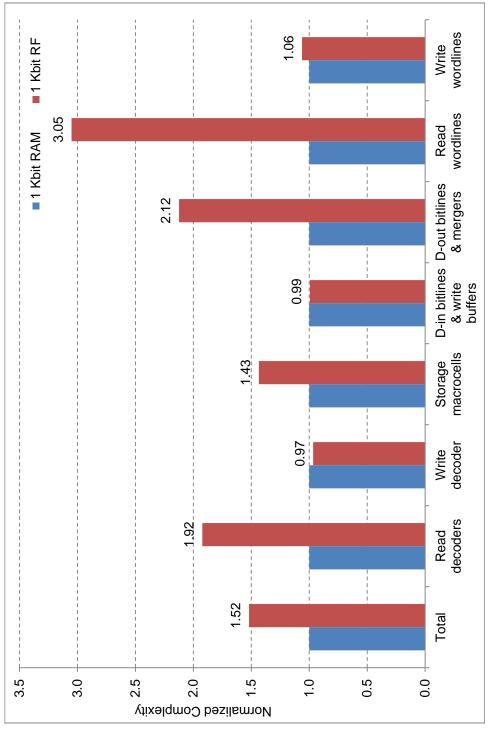

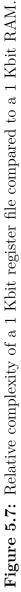

| 5.7  | Relative complexity of a 1 Kbit register file compared to a 1  |

|      | Kbit RAM                                                       |

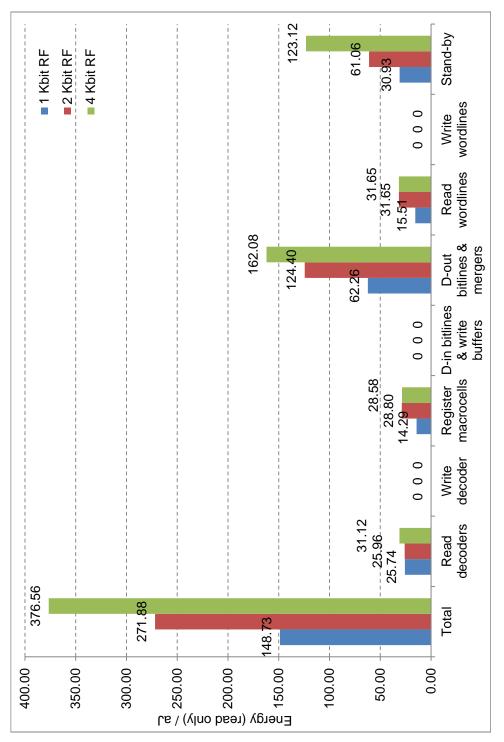

| 5.8  | Register file energy per read only operation                   |

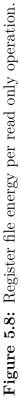

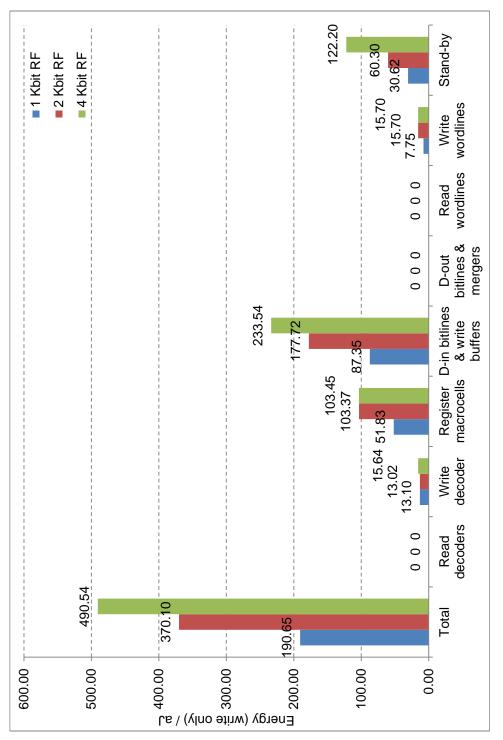

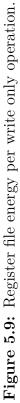

| 5.9  | Register file energy per write only operation                  |

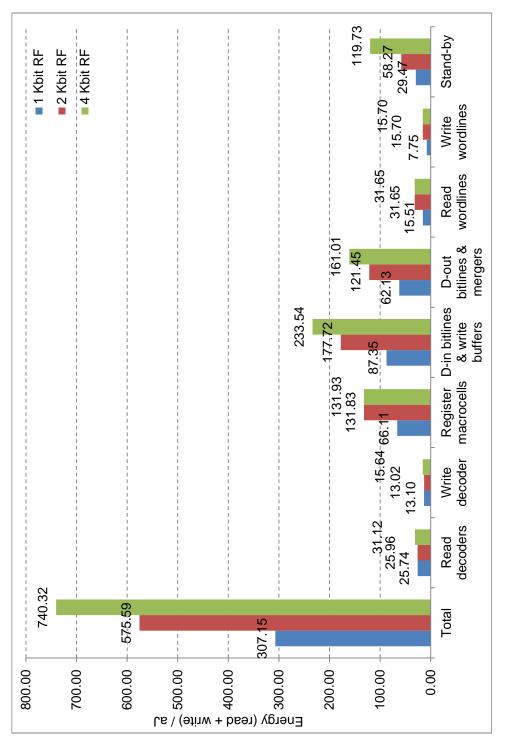

| 5.10 | Register file energy per read $+$ write operation              |

| 5.11 | Relative energy of a 1 Kbit register file compared to a 1 Kbit |

|      | RAM                                                            |

| 5.12 | Register file dynamic and stand-by energy breakdown 69         |

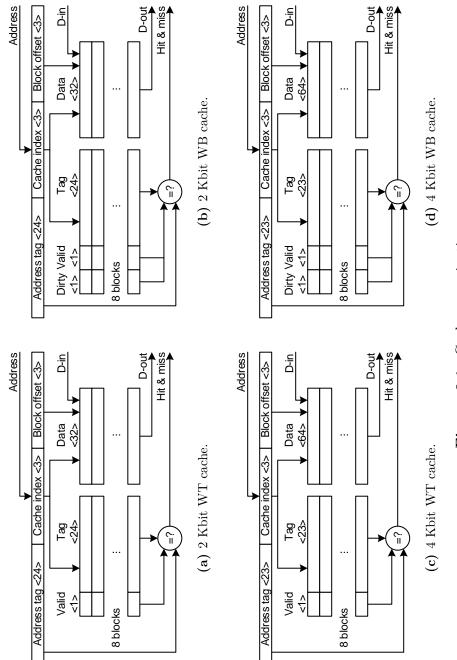

| 6.1  | Cache organization                                             |

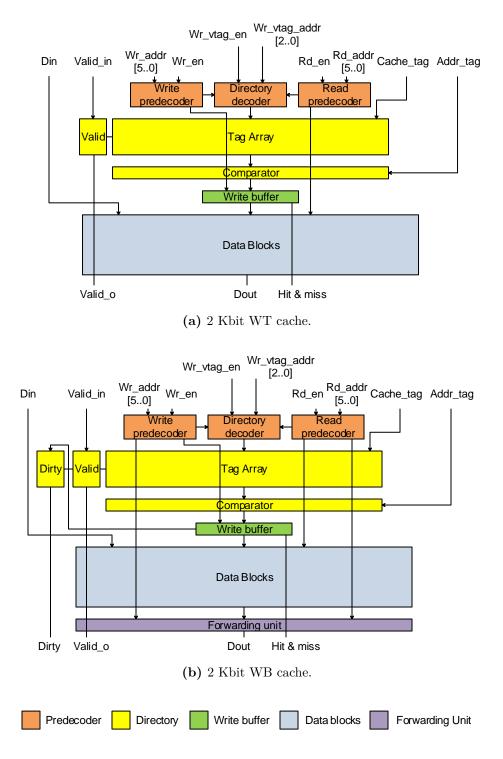

| 6.2  | Cache top-level structure                                      |

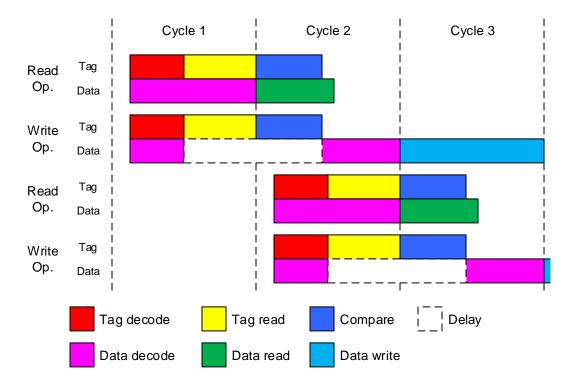

| 6.3  | Cache pipelines                                                |

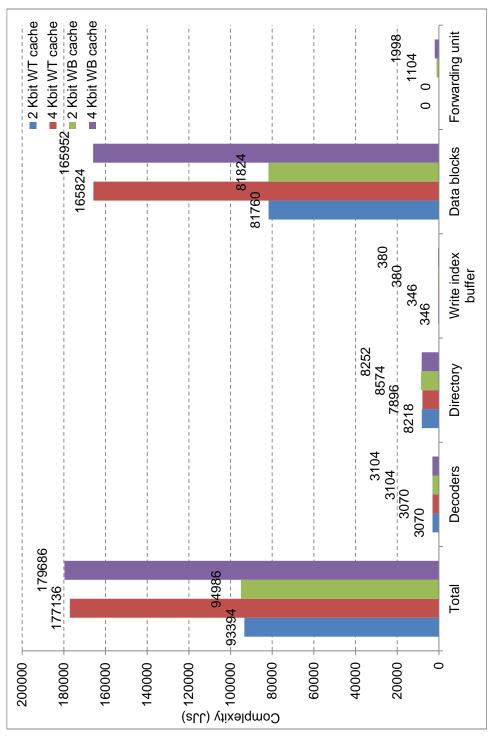

| 6.4  | Cache complexity breakdown                                     |

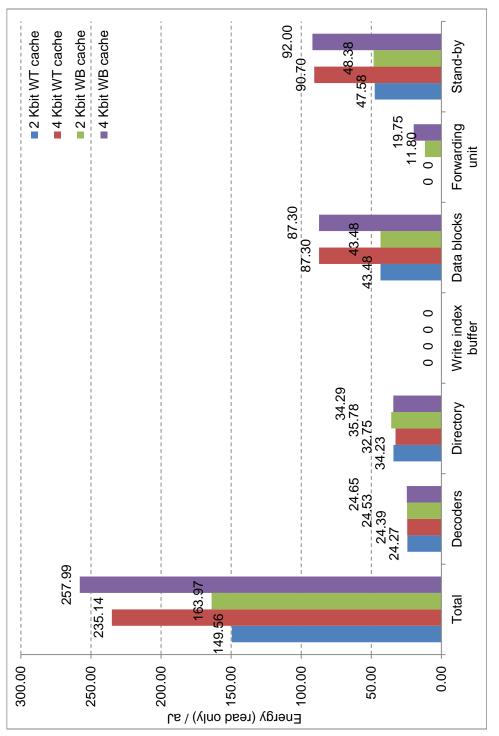

| 6.5  | Cache energy per read hit operation                            |

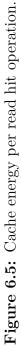

| 6.6  | Cache energy per write hit operation                           |

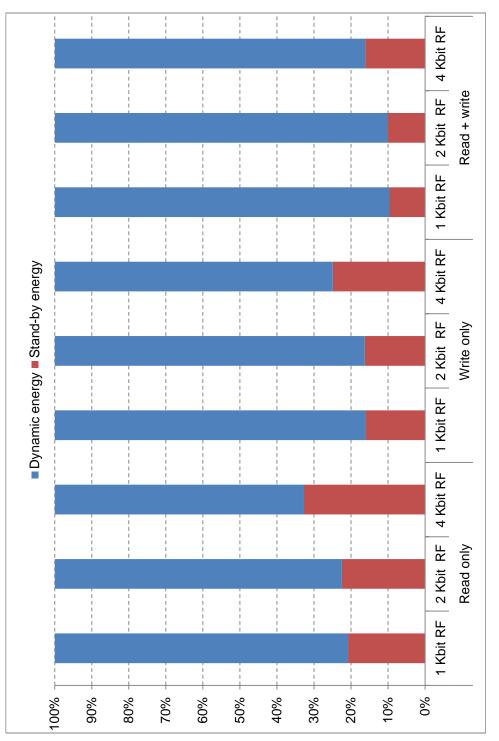

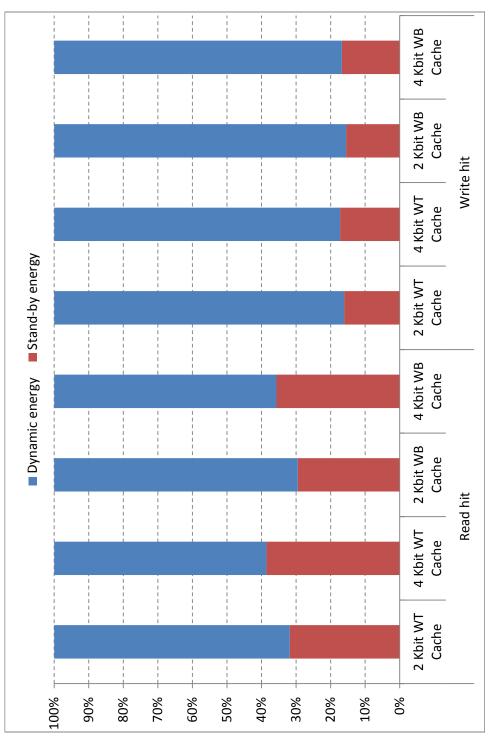

| 6.7  | Cache dynamic and stand-by energy breakdown                    |

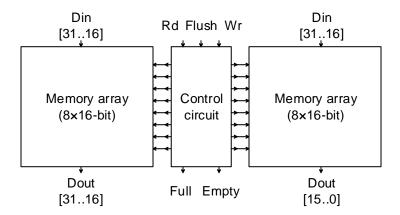

| 7.1  | Top-level structure of a 256 bit FIFO                          |

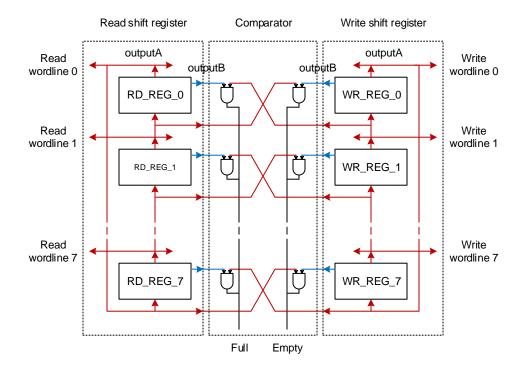

| 7.2  | The FIFO control circuit schematic (8-word version) 87         |

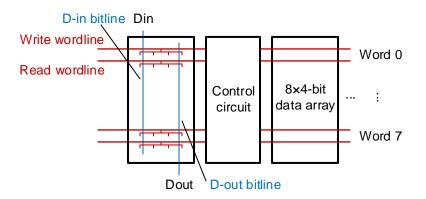

| 7.3  | The memory array schematic                                     |

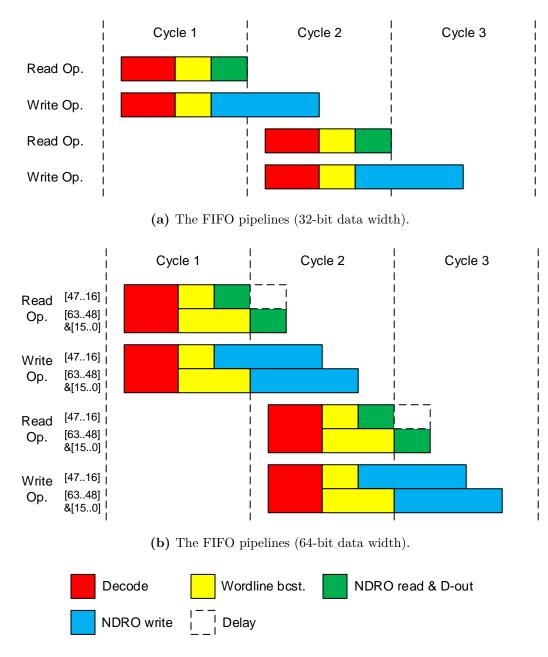

| 7.4  | The FIFO pipelines                                             |

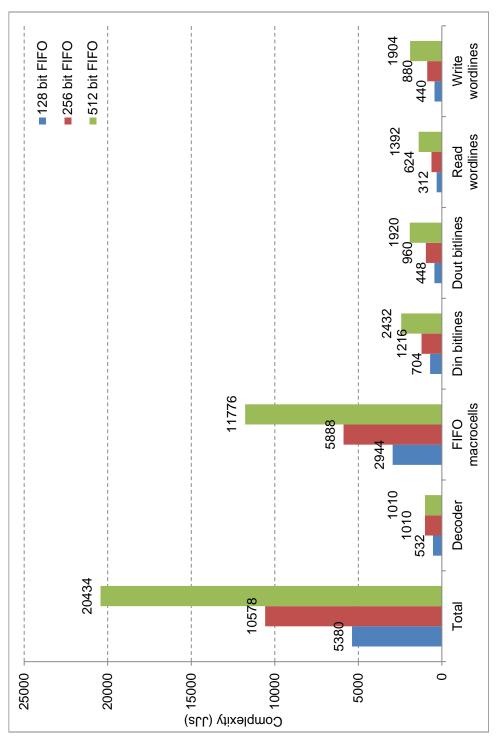

| 7.5  | FIFO complexity breakdown                                      |

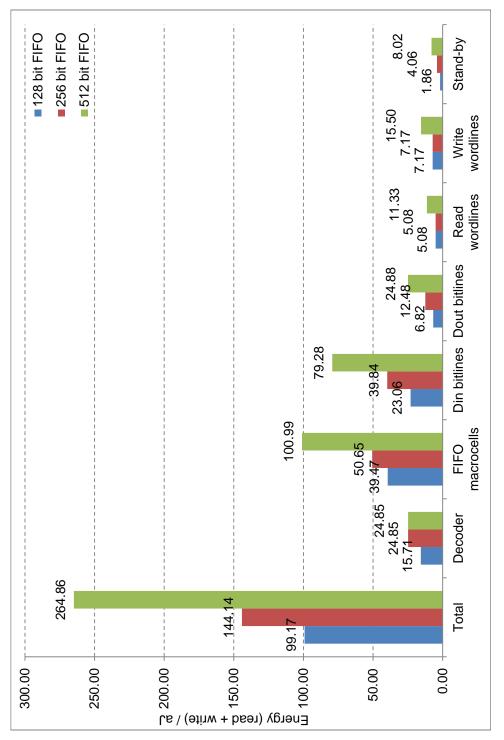

| 7.6  | FIFO energy per read + write operation                         |

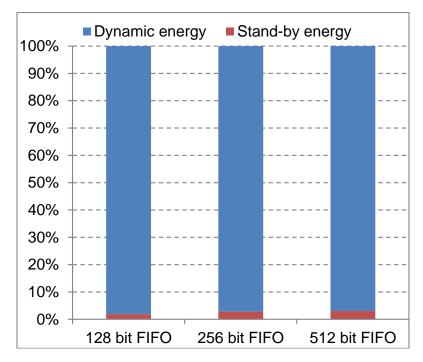

| 7.7  | FIFO dynamic and stand-by energy breakdown                     |

| 1.1  | The dynamic and brand by chergy breakdown                      |

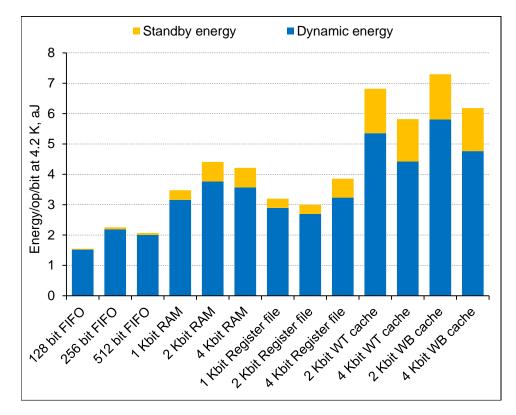

| 8.1 | The RQL storage energy consumption profile for the 248 nm                         |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | 100 $\mu$ A/ $\mu$ m <sup>2</sup> process with the min. $I_c = 38 \mu$ A at 4.2 K | 97 |

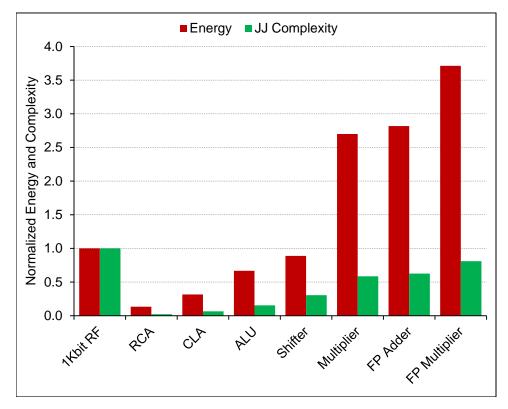

| 8.2 | Relative energy and JJ complexity of the 32-bit RQL processing                    |    |

|     | units compared to the 8.5 GHz 1 Kbit $32x32$ bit register file.                   | 98 |

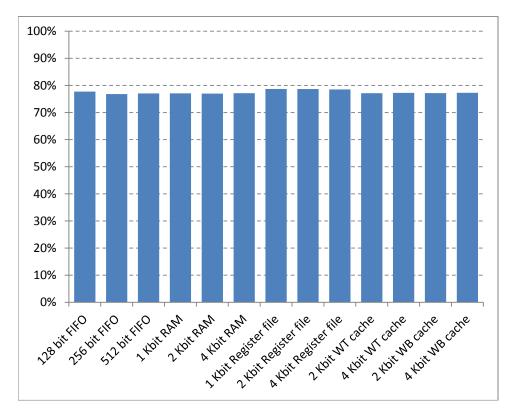

| 8.3 | The presentage of the connection cells to the total complexity                    |    |

|     | in terms of JJs                                                                   | 99 |

|     |                                                                                   |    |

# List of Tables

| 4.1 | Major RAM design components           | 37 |

|-----|---------------------------------------|----|

| 4.2 | Summary of the RAM designs            | 45 |

|     | RAM stand-by energy.                  | 53 |

| 5.1 | Major register file design components | 55 |

| 5.2 | Summary of the register file designs. | 60 |

| 5.3 | Register file stand-by energy         | 70 |

| 6.1 | Summary of the cache designs          | 78 |

|     | Cache stand-by energy                 | 84 |

| 7.1 | Summary of the FIFO designs           | 90 |

| 7.2 | FIFO stand-by energy.                 | 95 |

## Acknowledgments

This may be the most difficult section I need to write in this dissertation. Memories of happiness and frustration come back to me as I am trying to remember all the people I would like to acknowledge. I wish I do not leave anyone out. But for those I may have overlooked, I truly appreciate and enjoy our time together.

First and foremost I'd like to thank Prof. Mikhail Dorojevets, my advisor at Stony Brook University. His hands-on guidance, unrelenting conviction and strive for perfection has sharpened my skills and made this dissertation possible. Besides my research, Prof. Dorojevets always gives me a lot of advice on my academic progress and career. I am extremely grateful for that.

This dissertation could not be complete without the help of the other members in my committee: Prof. Sangjin Hong, Prof. Emre Salman and Prof. Jennifer Wong. I am very grateful for their feedback, patience and encouragement. Also, I thank Rachel Ingrassia and Susan Hayden of the Electrical and Computer Engineering department for helping me work through the labyrinth of paperwork and graduation process.

No research can be finished without the help of fellow colleagues. In the Ultra High Speed Computing Laboratory, I am very lucky to work with Dr. Christopher Ayala. He is a very nice and skillful person. He guided me into the research on Reciprocal Quantum Logic and helped me with all questions in the research and career. I cannot forget the time with Hao Chen, with whom I have completed the multiplier project in the lab. He also gave me a lot of information during my job hunting. I am looking forward to meet you in California in December. Thanks to Artur Kasperek, I wish you and your family all the best in Poland.

I would like to thank Prof. Alex Doboli and Cristian Ferent, who provided me a chance to work on analog circuit layout at the Mixed-Domain Embedded Systems Laboratory in my master's. To Qilin Miao, I had a great time with you in the lab, and you help me a lot when I was busy with computer architecture project and algorithm exams.

There are countless people I am grateful to in my undergraduate at Sun

Yat-sen University. As a freshman, I didn't know what to do and how to plan my future until Prof. Xiao Huang and Yanxiang Bao introduced me into the world of electrical design. After that, I decided to start my career as an electrical engineer. I met lots of friends during my study: Zongdie Li, Jinsong Mao, Kechao Huang and Chunhua Zhou. We worked together and learnt from each other. That was the most enjoyable time in my life.

The friendships I have forged during my graduate studies at Stony Brook University are very dear to me. I value the friendships of other fellow Ph.D students, Wenxiang Ding, Yang Liu, Jie Zhao, Fanshu Jiao, Qi Fan, Yifan Hu, Zongyuan Liu, Yutong Pang, Xinyu Zhang, Lei Wang, Huafeng Huang, etc. I thank each and every one of them for their outpouring support and wonderful memories.

And finally, I would like to thank my family and my girlfriend. To my parents, Lucheng Chen and Qiongjin Mo, thank you for your unending, nurturing love. To my grandfather Yongxi Chen and my Uncle Guoping Mo, thank you for your affection and education that have made me the person I am today. To my girlfriend, Yaqun Yu, thank you so much for standing beside me and support me during my busiest time.

Zuoting Chen Saint James, New York USA November 2015

### Vita

Zuoting Chen was born in Guangdong, China on February 7, 1989. He finished his B.S.E.E. program at Sun Yat-sen University, Guangdong, China in June 2011. In the same year, he was admitted into the M.S.E.E. program at Stony Brook University. In December 2012, he graduated from M.S.E.E. program and admitted into the Ph.D. program in Computer Engineering with a minor area in Circuits and VLSI at Stony Brook University. He passed the Computer Engineering Qualifying Exam in April 2013. Since July 2012, he has been working as a research assistant under Dr. Mikhail Dorojevets, conducting studies on superconducting Reciprocal Quantum Logic storage and processing units. He is a graduate student member of IEEE.

# **Publications**

The following is a list of publications that are a result of the research conducted for this dissertation:

- M. Dorojevets, Z. Chen, C. L. Ayala, and A. K. Kasperek, "Towards 32-bit Energy-Efficient Superconductor RQL Processors: The Cell-Level Design and Analysis of Key Processing and On-Chip Storage Units," *IEEE Transactions on Applied Superconductivity*, vol. 25, no. 3, Jun. 2015.

- 2. M. Dorojevets, Z. Chen, "Fast pipelined storage for high-performance energy-efficient computing with superconductor technology," in *IEEE Proc. Emerging Technologies for a Smarter World (CEWIT), 2015 12th International Conference Expo on*, pp.1-6, 19-20 Oct. 2015.

# Chapter 1

# Fundamentals of Superconductor Technology

#### Outline

| 1.1 | Intr  | oduction                                     | 1        |

|-----|-------|----------------------------------------------|----------|

| 1.2 | Jose  | phson Junctions                              | <b>2</b> |

| 1.3 | Rap   | id Single Flux Quantum Logic                 | 4        |

| 1.4 | Ene   | rgy-Efficient RFSQ Logic                     | 8        |

| 1.5 | Brie  | f Introduction to Other Superconductor Logic |          |

|     | Fam   | ilies                                        | 9        |

| 1.6 | Prio  | r Work on SFQ Logic                          | 10       |

|     | 1.6.1 | 100 GHz SFQ Bit-Serial Adder                 | 10       |

|     | 1.6.2 | Fujitsu's 8-bit DSP Microprocessor           | 10       |

|     | 1.6.3 | FLUX-1 Microprocessor                        | 11       |

|     | 1.6.4 | CORE1 Microprocessor                         | 13       |

|     | 1.6.5 | 20 GHz 8-bit RSFQ Frontier Datapath          | 14       |

### 1.1 Introduction

High-performance and energy-efficiency are the critical issues in modern digital integrated circuit design. Superconductor technology, with high operation speed and zero resistance at DC, has become one of the promising candidate for high-performance and energy-efficient computing. The essential element in the superconductor technology is a Josephson junction (JJ). A JJ is built according to the Josephson effect that was predicted by Brian David Josephson in 1962 [1, 2, 3] and experimentally confirmed in Bell Labs. In late 1960s, Josephson junction (JJ) was proved to be a suitable choice for fast circuit design. Without the need of doping materials, the fabrication technology for JJ-based integrated circuit was simpler than the fabrication technology for semiconductor [4]. The further improvements in the fabrication technology made the Josephson junction integrated circuits easier to fabricate. As demonstrated, some superconductor logic gates can operate at 770 GHz [5]. To provide a cryogenic environment for the superconductor circuit, a cryostat device is required to keep the circuit at the temperature of ~4.2 K. Even with the unavoidable high costs of cryo-cooling, superconductor technology has advantages over CMOS in terms of energy efficiency [6].

The remainder of this chapter provides an introduction of the superconductor technology family. A brief review of the prior work in this area is also given. In Chapter 2, we will focus on the concept of Reciprocal Quantum Logic (RQL), which is used in this research. A tunable RQL cell library and its target fabrication process are also included. Chapter 3 reviews the current status and challenges of the research on superconductor storage, as well as the opportunity of designing local storage units with RQL.

Four types of local storage units are studied in this research: 1) RAM with 1 read and 1 write ports in Chapter 4, 2) register file with 2 read and 1 write ports in Chapter 5, 3) write-through and write-back cache in Chapter 6, and 4) first-in first-out buffer in Chapter 7.

Finally, Chapter 8 makes some final discussions and conclusions of this research, follow by a brief outlook on further research in superconductor RQL local storage and processors.

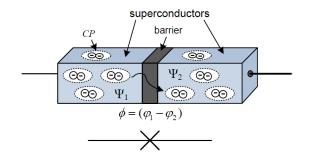

### **1.2** Josephson Junctions

A Josephson junction is a two-terminal device with two niobium superconductors separated by a thin aluminum oxide barrier, as shown in Figure 1.1 on page 3. The barrier is ~1-nm-thick so that both normal electrons and Cooper pairs can tunnel through [7, 8, 9]. Only Cooper pairs can tunnel when zero voltage is applied to a JJ; both Cooper pairs and normal electrons can tunnel when a voltage is applied across the junction. The fundamental relation between the phase drop  $\phi = \varphi_1 - \varphi_2$  and voltage drop  $V = \mu_1 - \mu_2$  in a JJ can be shown in Equation 1.1, where *h* is Planck's constant and *e* is the electron charge [10].

$$\frac{d\phi}{dt} = \left(\frac{2e}{h}\right)V(t) \tag{1.1}$$

**Figure 1.1:** Josephson junction structure and circuit symbol [15]. © 2011 IEEE.

The flow of Copper pairs (supercurrent) in a JJ can be determined by Equation 1.2, where  $\phi$  is the phase drop and  $I_c$  is the critical current of a JJ that depend on its area and barrier transparency [10].

$$I_s = I_c \sin \phi \tag{1.2}$$

For large signals, another three components should be taken in to account, as in Equation 1.3, where C is the junction capacitance and R is its "normal resistance" [10].  $I_f(t)$  is the current noise in R, which is very small.

$$I(t) \approx I_c \sin \phi + C \frac{dV}{dt} + \frac{V}{R} + I_f(t)$$

(1.3)

A JJ can operate in two different modes: voltage-state (latching) and single flux quantum (SFQ). Figure 1.2 on page 4 shows the I-V characteristics of these two modes[11, 12, 13]. In the first mode, as shown in Figure 1.2a on page 4, the junction switches from V = 0mV to  $V = V_g$  when the current exceeds  $I_c$ . The junction can be reset to zero-voltage stage when the current is reduced near zero. This two-state logic voltage approach was the first JJbased superconductor family and very popular for superconductor computing projects in IBM and Japan during 1970s and 1980s. In order to reset the junction to zero-voltage, this logic uses by AC power system. However, the demonstrations had shown that the speed of this technology was limited to about 1 GHz. This was the reason why IBM and other research groups stopped working with the latching logic technology in 1980s [14].

A Josephson junction can also operate in SFQ mode if the junction is shunted by a small resistor. The I-V curve is shown in Figure 1.2b on page 4. If the current is higher than  $I_c$ , the voltage can increase continuously. This approach is the fundamental of the Rapid Single Flux Quantum (RSFQ) logic, which will be discuss in the next section.

Figure 1.2: I-V characteristics of Josephson junction [11].

### 1.3 Rapid Single Flux Quantum Logic

Rapid Single Flux Quantum logic has been developed to increase the operation speed of JJ-based circuits. RSFQ circuits are based on JJs shunted by a resistor which allows JJ working at the SFQ mode. Moreover, RSFQ circuits are DC powered instead of AC powered in voltage-state logic. RSFQ circuit had been demonstrated at clock frequency of 100 GHz in 1980s.

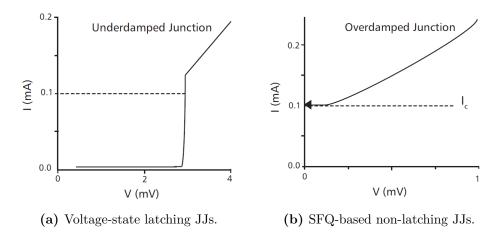

RSFQ uses the natural superconductor property that the current in a closed superconducting ring is the multiples of the magnetic flux quantum  $\Phi_0$ . RSFQ is based on the manipulation and transportation of these magnetic flux quanta [16]. The logical states '1' and '0' are represented by a presence and absence of a single flux quantum, respectively. Figure 1.3 on page 5 shows a simplest SFQ circuit, Superconducting QUantum Interference Device (SQUID), that is used to store the digital information. The SQUID is a superconductor ring interrupted by a JJ. The JJ plays a role of I/O interface by manipulating flux quanta inside the superconducting ring. If the current level is lower than the critical current  $I_c$ , the JJ allows a constant superconducting current (dc) to pass through without voltage drop and the phase difference between two superconductors remains constant. If the current exceeds  $I_c$ , a voltage across the junction is developed and a very short voltage pulse V(t) (so called SFQ pulse) is generated. The SFQ pulse is used to carry digital information and can travel through the circuit. Logical '1' is represented by the arrival of a SFQ pulse, and logical '0' is represented by the absence of SFQ pulses. Equation 1.4 shows the relationship between SFQ pulse and magnetic flux quantum, where h is Planck's constant and e is the electron charge.

Figure 1.3: Superconductor ring and SFQ pulse [16].

$$\int V(t)dt = \Phi_0 = \frac{h}{2e} \approx 2.07 \text{ mV} \times \text{ps}$$

(1.4)

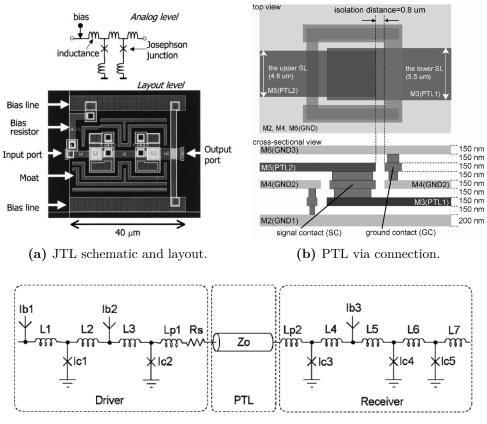

SFQ pulses can be transferred through two types of connections: 1) active Josephson junction transmission lines (JTL) and 2) passive transmission lines (PTL). Figure 1.4a on page 6 shows the simplest JTL. PTLs provide fast connections for long distance propagation of SFQ pulses at a velocity of ~100 µm/ps [17, 18, 19]. Active JJ-based drivers (TX) and receivers (RX) are required to amplify the pulse before sending over a PTL, and re-amplify it from the PTL, respectively. This is a propagation delay overhead for benefiting from the high-speed and low-loss transmission [20]. A driver-PTL-receiver schematic is shown in Figure 1.4c on page 6. As shown in Figure 1.4b on page 6, the ISTEC 10 kA/cm<sup>2</sup> advanced process supports two PTL layers [17].

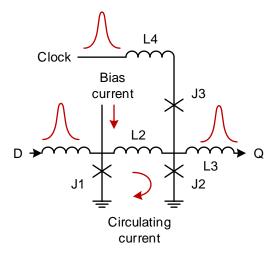

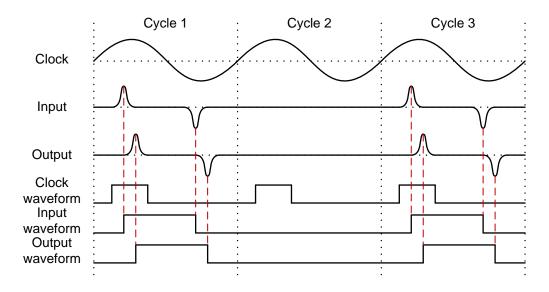

A RSFQ D flip-flop is shown in Figure 1.5a on page 7. A storage loop is formed by an input junction J1, an inductor and a junction J3. J1 is bias at  $0.7I_c$ . When an input SFQ pulse arrives at data input, the current in J1 will exceed the critical current, and J1 will switch and store one flux quantum into the loop. This flux quantum adds a current in J3. The arrival of a clock pulse will switch J3, generating an output SFQ pulse and resetting loop back to zero-state. If there is no flux quantum in the loop, the clock pulse cannot switch J3 because the current in J3 is insufficient. As the result, no SFQ pulse is generated at the output. Figure 1.5b on page 7 shows the RSFQ D flip-flop waveform.

Power dissipation in RSFQ has two parts: dynamic power and static power. The dynamic power comes from the energy loss during a junction switch, and the static power comes from the bias current distribution network that uses bias resistors to distribute the bias current to JJs. The major contribution of the power dissipation is the static power, which is ~99% of the total power in some large-scale designs [22]. The total power of RSFQ circuit can be

(c) Driver-PTL-Receiver schematic.

**Figure 1.4:** JTL and PTL connections used in superconductor logic [17, 21]. © 2009 IEEE.

(a) Circuit schematic.

(b) Circuit waveform.

Figure 1.5: RSFQ D flip-flop [1, 11, 15, 20].

estimated by Equation 1.5 at 4.2 K, where  $I_b$  is the total bias current and  $V_b$  is the bias voltage which is 2.6 mV for the HYPRES 4.5 kA/cm<sup>2</sup> process, and 2.5 mV for the ISTEC 10 kA/cm<sup>2</sup> process. To estimate the power consumption at room temperature, we need to take into account the power to cool the circuit down to 4.2 K, as shown in Equation 1.6, where  $1000W_{room}/W_{cryo}$  is the cryostat efficiency [20].

$$P_{cryo} = I_b V_b \tag{1.5}$$

$$P_{room} = P_{cryo} \left( 1000 \frac{W_{room}}{W_{cryo}} \right)$$

(1.6)

RSFQ logic has some serious weaknesses. One of them is the high static power consumption. As we mentioned above, the static power dissipated on bias resistors is significantly higher than the dynamic power. This can be a problem as the circuit complexity grows, which makes RSFQ unsuitable for energy-efficient VLSI design. To overcome this problem, several new logic families are developed to reduce the static power.

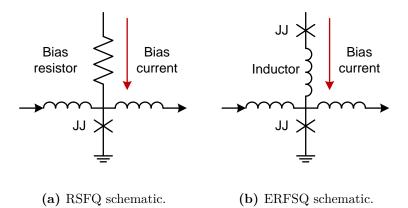

### 1.4 Energy-Efficient RFSQ Logic

Energy-efficient Rapid Single Flux Quantum (ERFSQ) logic is developed to reduce the static power consumption [22, 23]. Unlike RSFQ that uses bias resistors to supply a bias current, ERFSQ uses JJs (act like a natural current limiter) to distribute current to the logic gates, as shown in Figure 1.6 on page 9. To achieve this, the voltage on the power line must be equal or greater than the maximum possible DC voltage used to power the circuit [20]. This DC voltage is determined by the clock frequency, as shown in Equation 1.7, where  $f_c$  is the circuit clock frequency and  $\Phi_0 \approx 2.07$  mV × ps [23]. Equation 1.8 shows the ERSFQ power. Unlike the fixed 2.5-2.6 mV bias voltage in RSFQ, bias voltage in ERFSQ is in a range of 20-100 µV for clock frequencies in a range of 10-50 GHz.

$$V_b = \Phi_0 f_c \tag{1.7}$$

$$P = I_b V_b = I_b \Phi_0 f_c \tag{1.8}$$

Figure 1.6: Biasing in RSFQ and ERSFQ circuits [11].

### 1.5 Brief Introduction to Other Superconductor Logic Families

Besides ERFSQ, designer also developed some other SFQ logic families to eliminate the static power consumption in RSFQ. There are: 1) low-voltage SFQ [24], 2) reciprocal quantum logic (RQL) [25, 26, 27, 28, 29, 30, 31], and 3) adiabatic quantum-flux-parametron (AQFP) [32]. In this section, we will have a brief introduction to these new logic families.

Low-voltage SFQ reduces the static power by reducing the bias resistor in the bias current distribution network. The total power consumption is reduced by 93% compared to RFSQ. Simply reducing the bias resistor would decrease of the bias current, causing deterioration of the circuit operation and interaction between circuits. An LR-loading technique [33] is used to stabilize the circuit operation. With this approach, the static power consumption is reduced to the same level as the dynamic power consumption.

Reciprocal Quantum Logic is another new technology aims to reduce static power consumption. RQL uses AC power lines to drive the circuit, which also sever as a clock. RQL circuits with zero static power consumption have been demonstrated. This is the technology I am going to study in this research. More information will be in the next chapter.

AQFP is developed to reduce the dynamic power. It is an AC powered logic based on the quantum flux parametron (QFP) [34, 35, 36], which has the advantages of high-gain, high speed and high robustness. In AQFP, the QFP gates are working in adiabatic mode, which reduce the dynamic energy consumption to its fundamental limit.

### 1.6 Prior Work on SFQ Logic

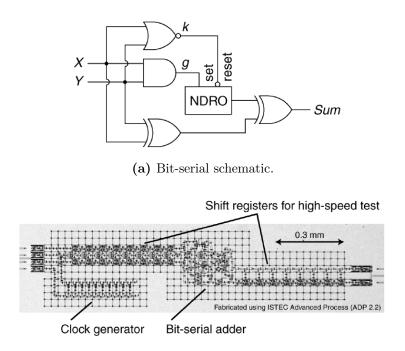

#### 1.6.1 100 GHz SFQ Bit-Serial Adder

A bit-serial RSFQ adder was developed by a reasearch group from Nagoya University, Yokohama National University, the Superconductivity Research Laboratory-ISTEC, and Kyoto University in 2011 [37]. This adder is targeted at the frequency of 100 GHz. Because multiple SFQ pulse cannot travel in the loop path, a concept of state transitions is adopted. A non-destructive readout (NDRO) gate is used to save the carry, as shown in Figure 1.7a on page 10. This circuit is based on the ISTEC 10 kA/cm<sup>2</sup> fabrication process and it has a sufficient DC bias margin of  $\pm 18\%$  at frequencies of up to 60 GHz. The correctness has been verified at the frequency of up to 93 GHz.

(b) Microphotograph of a bit-serial adder test circuit.

**Figure 1.7:** 100 GHz bit-serial adder [37]. © 2011 IEEE.

#### 1.6.2 Fujitsu's 8-bit DSP Microprocessor

Fujitsu Laboratories designed an 8-bit DSP microprocessor as one of the early approach to build practical chip using JJ technology in 1990 [14, 38]. This design is based on latching logic and has 23,000 JJs in a 5 mm  $\times$  5 mm chip. This DSP includes a 13-bit 16-function ALU [39], an 8-bit  $\times$  8-bit multiplier,

**Figure 1.8:** Microphotograph of Fujitsu's 8-bit DSP based on latching logic [14]. © 1992 IEEE.

a 64 word  $\times$  24-bit instruction ROM, a 16 word  $\times$  8-bit coefficient ROM, and two 16 word  $\times$  8-bit data RAM. The access time of the instruction ROM is 200 ps, and that of the RAM cells is 130 ps. The estimated frequency is up to 1 GHz and the power is 12 mW. At that time, it was about 100 times faster and one-tenth the power of conventional CMOS DSPs. All functions in this chip have been successfully demonstrated.

#### 1.6.3 FLUX-1 Microprocessor

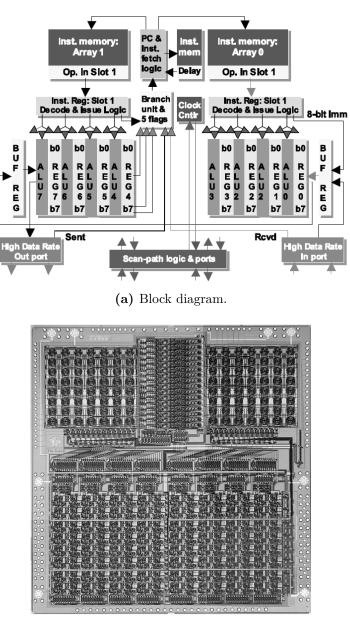

The FLUX-1 microprocessor was developed by Stony Brook University (SBU) and TRW (now Northrop Grumman) with the target frequency of 17-20 GHz [11, 40, 41, 42]. The goal was to study and understand the architectural and design challenges for 20+ GHz RSFQ processors. This 8-bit RSFQ microprocessor employs partitioned synchronous dual-op Long-Instruction-Word (LIW) architecture. The last version of the processor, FLUX-1R, was fabricated in TRW's 4 kA/cm<sup>2</sup>, 1.75 µm Josephson junction technology in 2002. This chip has 63,107 Josephson junctions on a 10.35 mm × 10.65 mm<sup>2</sup> die and the energy consumption is ~9.5 mW at 4.2 K. The block diagram and the physical layout are shown in Figure 1.9 on page 12.

Only a low-capacity instruction memory was implemented in this design. The memory has the following features:

(b) Microphotograph of the second chip.

Figure 1.9: The FLUX-1 8-bit RSFQ microprocessor [40]. © 2003 IEEE.

- There are 2 16-row  $\times$  16-bit arrays in the memory.

- Each arrays issues one instruction to the instruction register per cycle.

- Wave pipelining is used in the memory to ensure one dual-op instruction per cycle.

- The complexity of the memory is ~16,500 JJs, and takes over 25% of the total JJs complexity (not including PC and instruction fetch circuit).

#### 1.6.4 CORE1 Microprocessor

The CORE1 is a joint project by Nagoya University, and Yokohama National University, and Communications Research Laboratory at Kobe, and International Superconductivity Technology Center (ISTEC) Superconductor Research Lab (SRL) at Tsukuba [43, 44, 45, 46].

This project started with a simple processor known as CORE1 $\alpha$  which was fully demostrated in 2003. It has the following features [43]:

- A 32 byte shift-register-based memory for instructions and data.

- Two 8-bit data registers and a bit-serial ALU.

- Seven 8-bit instructions in the instruction set.

- Non-pipelined processing and control logic.

- 1 GHz system clock and 16-21 GHz local clock.

- $\sim 7,220$  JJs on a  $3.4 \times 3.2$  mm<sup>2</sup> die.

- Power consumption of 2.3 mW at 4.2 K.

In 2007, a more advanced version, CORE1 $\beta$  was demonstrated with the following features [44]:

- A 16-bit instruction register (IR).

- Four 8-bit register file.

- Two cascaded bit-serial ALUs.

- ~9,498 JJs.

- Power consumption of 3.0 mW at 4.2 K.

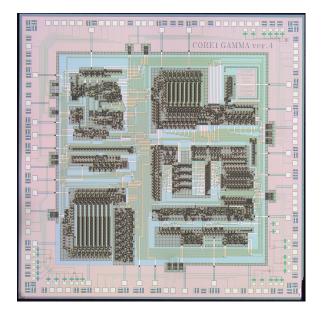

The final version,  $CORE1\gamma$ , is implemented with cache memory and pipeline techniques [46](Figure 1.10 on page 14).

• 16 byte and 8 byte shift-register-based direct-mapped instruction cache and data cache, respectively.

Figure 1.10: Microphotograph of the CORE1 $\gamma$  8 × 8 mm<sup>2</sup> chip [46].

- Eight-stage pipeline.

- 22,302 JJs on  $6.36 \times 6.36$  mm<sup>2</sup> area on an  $8 \times 8$  mm<sup>2</sup> die.

- Estimated power consumption of 6.56 mW at 4.2 K.

#### 1.6.5 20 GHz 8-bit RSFQ Frontier Datapath

An 8-bit RSFQ datapath has been developed in a joint project between SBU and HYPRES. This 8-bit datapath is based on a 32-bit Frontier data-flow microarchitecture developed at SBU [47]. The complete cell-level datapath design and its verification have been done by the SBU team using a SBU VHDL cell library tuned to the HYPRES 1.5  $\mu$ m 4.5 kA/cm<sup>2</sup> fabrication process. The HYPRES team developed the physical layout design, fabricated and tested two datapath components, namely an asynchronous wave-pipelined ALU [48, 49] and an 8 × 8-bit multi-port register file [50]. This NDRO-based register file can perform two simultaneous read operations and one write operation.

The ALU has been demonstrated at the target frequency of 20 GHz with  $\pm 5\%$  DC bias margins and the register file has been demonstrated at a low frequency with  $\pm 4\%$  DC bias margins.

# Chapter 2

# **Reciprocal Quantum Logic**

#### Outline

| 2.1 Overview                                                      | 5        |

|-------------------------------------------------------------------|----------|

| 2.2 Josephson Transmission Line in RQL 1                          | 7        |

| 2.3 Four-Phase Clocking 1                                         | 8        |

| 2.4 Other Key RQL Cells                                           | 0        |

| 2.4.1 Passive Transmission Line Receiver                          | 20       |

| 2.4.2 AndOr Gate                                                  | 21       |

| 2.4.3 AnotB Gate                                                  | $^{21}$  |

| 2.4.4 Set/Reset Gate $\ldots 2$                                   | 22       |

| 2.4.5 Non-Destructive Read-out Single-Bit Storage Cell $\ldots$ 2 | 23       |

| 2.5 Fabricated RQL Design                                         | <b>4</b> |

| 2.6 SBU RQL VHDL Cell Library 2                                   | 6        |

| 2.6.1 Clock Model                                                 | 26       |

| 2.6.2 Data Signal Model                                           | 27       |

| 2.6.3 Acknowledgements                                            | 28       |

| 2.7 Target Fabrication Technology 2                               | 8        |

### 2.1 Overview

Reciprocal Quantum Logic (RQL) [25, 26, 27, 28, 29, 31] is a new generation of superconductor SFQ logic that is currently considered as one of the solutions for high-performance energy-efficient computing. In this chapter, we will first discuss the fundamental of RQL, and the finished work with RQL. After that,

the SBU RQL cell library and fabrication process in Massachusetts Institute of Technology Lincoln Laboratory (MIT LL) that is used in this research will be provided.

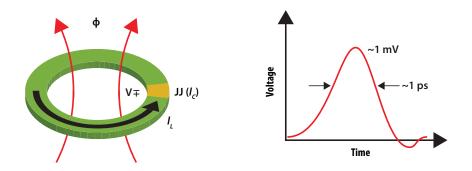

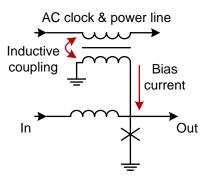

Unlike RSFQ, RQL is powered by AC power lines inductively coupled with the cells in series, as shown in Figure 2.1 on page 17. This AC power line is also serves as a clock to the circuit [25]. Without bias resistors, RQL have approximately two orders of magnitude better energy efficiency than similar superconductor circuits implemented with the older Rapid Single Flux Quantum (RSFQ) logic.

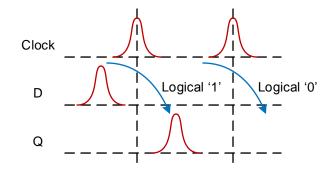

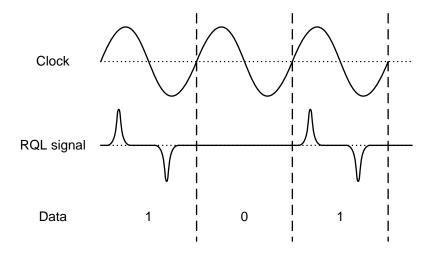

Figure 2.2 on page 17 shows how data are encoded in RQL. Logical '1' is represented by a pair of SFQ pules: a positive pulse during the positive half cycle follow by a negative pulse during the negative half cycle. The positive pulse is used to set the SQUID to '1' state and then propagate forward, while the negative pulse is used to reset the SQUID to '0' state, preventing signal from traveling backward [27]. Because the circuit can be reset by the following negative pulse, the trailing reset wave that is necessary in RSFQ is not required in RQL. This simplifies the gate design and creates a combinational logic behavior similar to CMOS.

The dynamic power consumption in RQL circuit is defined as the number of junction switch when a pair of positive and negative pulses arrives. As shown in Equation 2.1, where n is the number of switched JJs,  $I_c(i)$  is the junction's critical current, and f is the frequency.

$$P_{dynamic} \approx \frac{2}{3} \sum_{i=1}^{n} I_c(i) \Phi_0 f \tag{2.1}$$

In addition to the dynamic energy, RQL circuits have very small power consumption due to the parasitic coupling of clock lines to the JJ shunt resistors of the inactive cells in a stand-by mode of operation with no input pulses received during a cycle time [29]. We call it standby power consumption to distinguish it from the static power consumption in bias resistors of RSFQ cells. The accuracy of the energy model used in our simulation tools is expected to be within 10%.

In contrast to CMOS, the interconnect energy consumption does not depend on wire lengths because of the ballistic propagation of pulses with the speed of  $\sim 0.1 \text{ mm/ps}$  over superconducting Nb PTLs with negligible dielectric losses. Energy losses in passive microwave components are not considered in our study.

Figure 2.1: RQL schematic.

Figure 2.2: Data in RQL.

### 2.2 Josephson Transmission Line in RQL

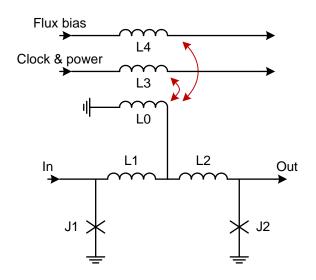

A RQL JTL is formed by a series of connection cells. A connection cell is an inductive loop formed by junctions J1 and J2 and inductors L1 and L2, as shown in Figure 2.3 on page 18. L0 is coupled to L3 in the AC power line to provide bias current through the junctions. The AC power line provides positive bias current during the positive half of the clock cycle and negative bias current during the negative half of the clock cycle, which is sufficient for positive and negative SFQ pulses to switch the junctions, respectively. An additional DC flux is used to induce a flux of  $\Phi_0/2$  in the connection cell, so the cell can switch between two symmetric states:  $+\Phi_0$  and  $-\Phi_0$ .

The connection cell can be used to amplify the pulse energy. This is achieved by stepping up the critical current of the cell from one to the next. The connection cell in JTL can amplify SFQ pulse energy by stepping up the critical current from one cell to the next. By increasing the critical current at a factor of  $\sqrt{2}$ , the SFQ pulse energy is doubled [27]. With this feature, JTL can be used as a SFQ splitter with fan-out of 2.

(a) Circuit schematic.

Figure 2.3: RQL connection cell [27].

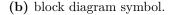

### 2.3 Four-Phase Clocking

A SFQ pulse can propagate through the connection cells as long as the bias current is sufficient [27]. During the negative half-cycle, the SFQ pulse that propagates forward in the positive half-cycle can move backward. To resolve this issue, RQL uses four-phase clocking: two clock lines with the phase difference of  $\pi/2$ . A connection cell can be coupled with one of the clock line in

Figure 2.4: Four-phase clocking in a RQL one-cycle delay register [27].

a wound or counter wound faction. This produces a total of four phases with the difference of 0,  $\pi/2$ ,  $\pi$ , and  $3\pi/2$  as shown in Figure 2.4 on page 19. When one phase is reaching the end of the phase, the next phase has already started in the next connection cell, allowing pulse propagation to continue. [27]

The SFQ pulse is self-synchronized in four-phase clocking. When a pulse reach a phase boundary (where the next connection cell is clocked by next phase), the pulse can wait for the start of the next phase and continue propagation. With this feature, pulses with different arrival times can be synchronized at the phase boundary without additional synchronize circuit.

In addition, several connection cells can be clocked with the same phase, as shown in Figure 2.5 on page 20. The SFQ pulse can travel through the connection cells in the same phase until it reaches the end of the phase's timing window [27]. The number of connection cells that can be set in one phase is determined by the phase time (clock period / 4) and the propagation delay through the connection cells. Total propagation delay through the connection cells cannot exceed the phase time.

Figure 2.5: Several RQL cells in a same phase [27].

## 2.4 Other Key RQL Cells

### 2.4.1 Passive Transmission Line Receiver

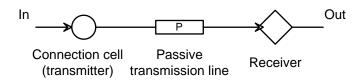

All superconductor circuits use lossless passive transmission lines (PTLs) to transmit SFQ pulses (without any capacitive charging involved) over long distance connections. As shown in Figure 2.6 on page 20, a connection cell (acting as a driver) sends a SFQ pulse to PTL. A PTL receiver receives and re-amplifies the pulse from the PTL. Like a connection cell, a PTL receiver should be inductively coupled with the clock & power line and set to one of the four phases in a clock cycle. To be safely received by a PTL receiver, a pulse from a passive transmission line needs to arrive during the PTL reception window, which is in the center of a phase and the width is one eighth of a clock cycle (half phase).

Figure 2.6: Receiver and passive transmission line.

### 2.4.2 AndOr Gate

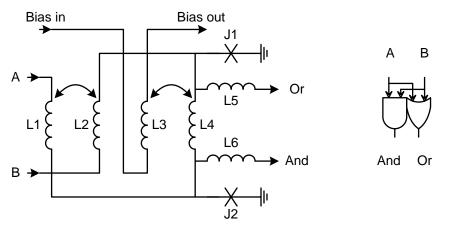

The schematic of an AndOr gate is shown in Figure 2.7a on page 21, J1 at the OR output is preferentially biased by  $\Phi_0/2$ . This junction will switch when the first pulse arrives at either input. After switching, a pulse is generated at Or output and the flux state of the gate is reversed, which means J2 is preferentially biased. If the second pulse arrives, J2 will switch and a pulse will be generated at And output. If two pulses arrive simultaneously, J1 and J2 switch and generate Or and And output at the same time. The AndOr gate symbol is in Figure 2.7b on page 21.

(a) AndOr gate schematic.

(b) AndOr gate symbol.

**Figure 2.7:** AndOr gate [27].

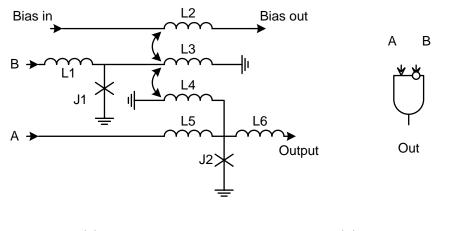

### 2.4.3 AnotB Gate

Figure 2.8a on page 22 shows the schematic of an AnotB gate. A pulse arrives at B switches J1, creating a negative current that block J2 from switching. This is so call output-inhibiting state, as a pulse at A cannot propagate to the output. This state will be cancelled out by the following reciprocal pulse after half cycle. If there is no input pulse at B, pulse arrives at A can switch J2 and generate output. There is a timing requirement for the AnotB gate: pulse at B should arrive earlier or simultaneously with pulse at A. The AnotB gate symbol is in Figure 2.8b on page 22.

Both AndOr and AnotB gates are unclocked. The bias current is supplied by the connection cells that drive the input SFQ pulse to or receive the output pulse from it. As the result, these gates can be place either in one phase or in

**Figure 2.8:** AnotB gate [27].

the boundary of two phases. The timing of the gate depends on the connection cell that supplies bias current to it.

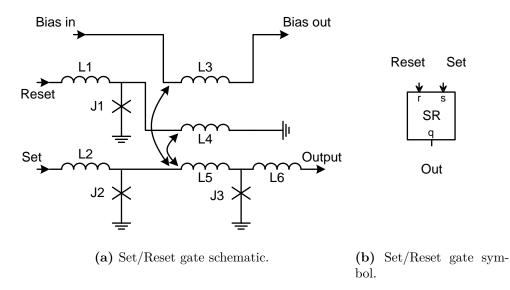

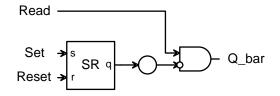

### 2.4.4 Set/Reset Gate

The Set/Reset gate is used to build the basic storage device with non-destructive readout in RQL. Figure 2.9a on page 23 shows the schematic of a Set/Reset gate. J2, J3 and L5 form a set memory loop, and J1 and L4 form a reset loop. This gate has an internal state that can be switch between two bi-stable flux states, which represent logical '1' and '0'.

Initially, the internal flux of the gate is  $+\Phi_0/2$ . If a pair of pulses arrives at Set port, the positive pulse applies  $+\Phi_0$  to the gate and the internal flux is  $+3\Phi_0/2$ . Then J3 switches and generates a positive output and the internal flux is return to  $+\Phi_0/2$ . The following reciprocal pulse changes the internal flux to  $-\Phi_0/2$ . Any further pairs of pulses will change the internal flux to  $+\Phi_0/2$  and back without output. We can define this as state '1' [27].

A pair of pulses that arrives at Reset can change the state of the gate. The leading positive pulse applies  $-\Phi_0$  to the gate and changes the internal flux to  $-3\Phi_0/2$ . A negative output is generated and the internal flux is return to  $-\Phi_0/2$ . The reciprocal pulse changes the internal flux to  $+\Phi_0/2$ . The internal flux keeps switching between  $-\Phi_0/2$  and  $+\Phi_0/2$  for following reset pulse pairs until a pair of pulses arrives at Set input. We can define this as state '0' [27].

The Set/Reset gate symbol is shown in Figure 2.9b on page 23.

**Figure 2.9:** Set/Reset gate [27].

In order to allow negative output to propagate, the reset pulse should arrive at the negative clock cycle. As the result, the gate should operate in two phases, where Set input and output are in the same phase and Reset input is in another.

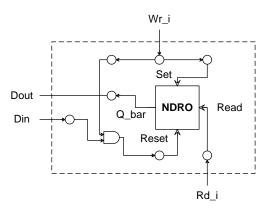

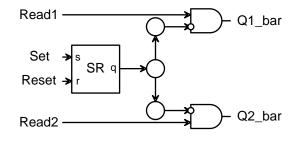

### 2.4.5 Non-Destructive Read-out Single-Bit Storage Cell

The Set/Reset gate only generates output when the internal flux state is changed. To preserve the output from the Set-Reset gate, Non-Destructive Read-Out (NDRO) single-bit storage cell is developed to preserve the output from the Set-Reset gate for multiple read operations, as shown in Figure 2.10 on page 24. The positive pulse (cause by set operation in the Set/Reset gate) from the Set/Reset gate can be stored in the connection cell until a negative reciprocal pulse (cause by reset operation in the Set/Reset gate) arrives. If there is a positive pulse stored in the connection cell, the AnotB gate is in output-inhibiting state. The pulses from read input will not generate an output. In other words, a logical '0' is read. If there is no positive pulse stored in the connection cell, pulse stored in the connection cell, the AnotB gate. In this case, a logical '1' is read.

Figure 2.10: Non-destructive read-out storage cell schematic [27].

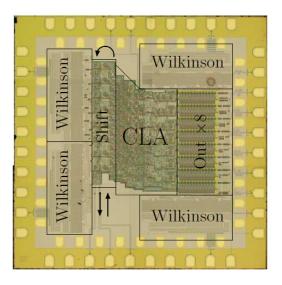

### 2.5 Fabricated RQL Design

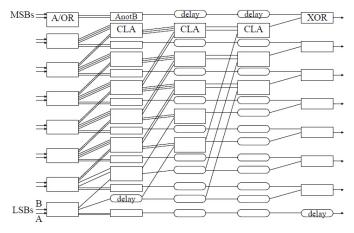

An RQL 8-bit carry look-ahead adder is designed by Northrop Grumman System Corp. in 2013 [28]. This is the first processing unit implemented and demonstrated with RQL technology.

This RQL carry look-ahead adder is implemented with the Kogge-Stone radix-2 structure. It contains  $log_2N + 2$  stages for an N-bits input as shown in Figure 2.11a on page 25. The first stage generates the prefix signals such as carry propagate and carry generate signals. The following module is the  $log_2N$  stages carry look-ahead network. In the final stage, the result is computed.

The latency of this adder is 150 ps (not including clock skew) at the clock frequency of 10 GHz, and the power dissipation is only 510 nW at 6.2 GHz. Figure 2.11b on page 25 shows the fabricated CLA chip on a  $5 \times 5 \text{ mm}^2$  die.

(a) Kogge-Stone CLA Structure.

(b) Kogge-Stone CLA microphotograph.

Figure 2.11: 8-bit Kogge-Stone CLA [28]. © 2013 IEEE.

## 2.6 SBU RQL VHDL Cell Library

In order to design and evaluate large-scale RQL circuit, simulation tools needs to be developed. A tunable RQL cell library was developed in the Ultra High Speed Computing (UHSC) Laboratory at Stony Brook University. This cell library logically models RQL circuits and provides functions for researchers to do cell level implementation, verification and statistic analysis for large-scale designs. Since the physical design tools and fabrication process is not available at this time, this library focuses on the layout-aware cell level design and provides design statistics that close to a completed physical design. Additional CAD tools are necessary to finish the physical design in the future.

All RQL cells are described using VHDL behavioral models with truth tables or finite state machines. Physical features such as energy consumption, JJs complexity, latency and approximate size are specified and tuned to the target fabrication process.

The cells have built-in functions to check any timing violations during simulation and report them. The timing violation report contains important information such as when and where the violation occurred, what kind of timing constraint is violated (the signals arrive too early or too late). This is helpful for a logic level designer to identify the source of the violation and figure out the best solution to resolve it.

Switching activity of all cells is recorded during simulation and used to calculate dynamic power consumption. The library also provides functions for designers to obtain the design complexity in terms of JJs.

The design approach is successfully used in the joint work with HYPRES, Inc. on the development and demonstration of several 20 GHz RSFQ chips [48, 49, 51].

In this research, the cell library is tuned to the 248 nm 100  $\mu$ A/ $\mu$ m<sup>2</sup> fabrication process from MIT Lincoln Lab. The features of this fabrication process will be provided in the next section.

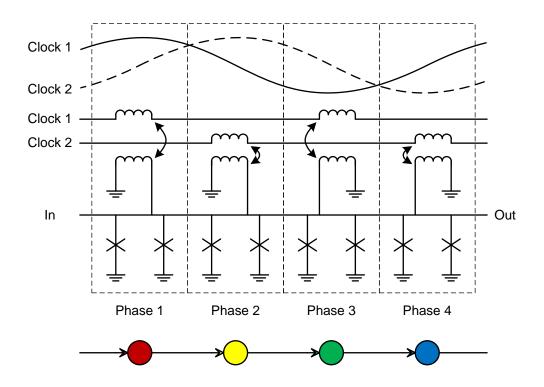

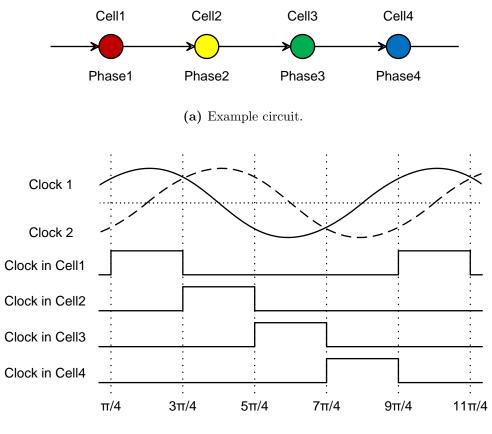

### 2.6.1 Clock Model

As discussed in before, there are two clock & power lines in RQL, and cells that inductive coupled with clock & power lines can be set to one of the phases in a clock cycle. A cell can only process RQL pulses during the phase that it has been set. To describe this feature in the simulation, the library use standard logic '1' in VHDL to present the valid phase, and standard logic '0' to present other invalid phases. Figure 2.12a on page 27 shows an example circuit and the clock signals of each cell in the VHDL model. There are four cells in the example circuit, and are set to phase 1 (red), 2 (yellow), 3 (green), 4 (blue).

(b) Simulation waveforms of the clock signal.

Figure 2.12: Clock signal in VHDL model.

For Cell1 in phase 1, the clock signal is standard logic '1' from  $\pi/4$  to  $3\pi/4$ , which means can process SFQ pulse during this time. For Cell2, Cell3, Cell4, the valid time to process signal are between  $3\pi/4$  and  $5\pi/4$ ,  $5\pi/4$  and  $7\pi/4$ ,  $7\pi/4$  and  $9\pi/4$ , as shown in Figure 2.12b on page 27. This definition simplifies the behavioral of the clock and the timing violation checking.

### 2.6.2 Data Signal Model

As the data in RQL are represented by pulses (unlike voltage level in CMOS), a new definition is set up to represent data signals in SFQ pulse based circuits: the rising-edge is used to represent a positive pulse, and the falling-edge is used to represent a negative pulse, as shown in Figure 2.13 on page 28.

Figure 2.13: Data signal in VHDL model.

### 2.6.3 Acknowledgements

The SBU RQL VHDL cell library is a work finished by past and present members in the UHSC laboratory, Stony Brook University under the direction and supervision of Dr. Mikhail Dorojevets. The contributors are:

- Christopher Ayala (Major developer): Involved in all aspects of library development, including implementation, testing, documentation, and maintenance.

- Artur Kasperek: Implemented some gate-level FSMs and built-in functions.

- Kruti Shah and Prachi Bemalkhedkar: involved in the library documentation.

- Zuoting Chen (dissertation author): Implemented some additional features and built-in functions.

## 2.7 Target Fabrication Technology

The Massachusetts Institute of Technology Lincoln Laboratory has developed a fully planarized  $100\mu A/\mu m^2$  process for very large scale integration (VLSI) SFQ circuit fabrication [52]. Figure 2.14 on page 29 shows several nodes of this fabrication process. This process is tune to support the development

| Fabrication Process Attribute     | ✓                               | ✓                               | Process Node     |                  |                  |

|-----------------------------------|---------------------------------|---------------------------------|------------------|------------------|------------------|

|                                   | SFQ3ee                          | SFQ4ee                          | SFQ5ee           | SFQ6ee           | SFQ7ee           |

| Critical Current Density (μΑ/μm²) | 100                             | 100                             | 100              | 100              | 100              |

| JJ diameter (surround) (nm)       | 700 (500)                       | 700 (500)                       | 700 (300)        | 500 (200)        | 500 (200)        |

| Number of superconducting layers  | 4                               | 8                               | 10               | 10               | 10               |

| Line width (space) (nm)           | 500 (1000)                      | 500 (700)                       | 350 (500)        | 250 (300)        | 180 (220)        |

| Metal thickness (nm)              | 200                             | 200                             | 200              | 200              | 150              |

| Dielectric thickness (nm)         | 200                             | 200                             | 200              | 200              | 180              |

| Resistor width (space) (nm)       | 1000 (2000)                     | 1000 (1000)                     | 700 (700)        | 500 (500)        | 350 (350)        |

| Resistor value (ohms per square)  | 2                               | 2                               | 2 and 0.002      | 2 and 0.002      | 2 and 0.002      |

| Via diameter (surround) (nm)      | 700 (500)                       | 700 (500)                       | 500 (350)        | 350 (250)        | 350 (200)        |

| Via type                          | Etched,<br>Stacked<br>Staggered | Etched,<br>Stacked<br>Staggered | Stud,<br>Stacked | Stud,<br>Stacked | Stud,<br>Stacked |

| Process Development               | Complete                        | Advanced                        | Underway         | Underway         | Underway         |

| Early Access Availability         | 2013                            | Now                             | 2015             | 2016             | 2017             |

| Primary Process                   | Now                             | Sep. 2014                       | 2016             | 2017             | 2018             |

**Figure 2.14:** MIT LL SFQ process [52]. Resent publication shows that SFQ5ee has 9 Nb superconducting layers [54].

of energy efficient circuit in the IARPA Cryogenic Computing Complexity (C3) program [53]. The process nodes, SFQ3ee and SFQ4ee with 4 and 8 superconducting layers, respectively, are already completed. Some advance process nodes (SFQ5ee, SFQ6ee, and SFQ7ee) with more superconducting layers and smaller JJ size are under development.

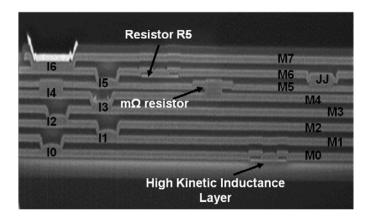

The SBU VHDL RQL cell library is tuned to the SFQ5ee process with 248 nm minimum feature size, 700 nm minimum JJ size, and 9 Nb superconducting layers (Figure 2.15 on page 30). The minimum JJ critical current is 38 µA. Compared to the earlier nodes, this process has smaller metal layer linewidth as well as etched via size. An additional high kinetic inductance superconducting layer is added below the first Nb layer M0 to enable compact bias inductors. A resistive layer is added to support interlayer sandwich-type resistors between Nb layers M4 and M5 [54].

Figure 2.15: Cross section of the SFQ5ee process [54].

## Chapter 3

# Superconducting Memory and Research Goals

### Outline

| 3.1        | Brie  | f Review of Superconducting Memory              | <b>31</b> |

|------------|-------|-------------------------------------------------|-----------|

|            | 3.1.1 | Wholly SFQ memory                               | 32        |

|            | 3.1.2 | Hybrid Josephson-CMOS Memory                    | 32        |

|            | 3.1.3 | JJ-MRAM                                         | 33        |

| <b>3.2</b> | New   | Opportunities in Energy-Efficient Local Storage |           |

|            | Unit  | s Design with RQL                               | <b>34</b> |

| <b>3.3</b> | Rese  | earch Goals                                     | <b>35</b> |

## 3.1 Brief Review of Superconducting Memory

The development of reliable, dense and fast energy efficient cryogenic memory remains to be one of the most serious challenges for superconductor computing. There have been several efforts to design such memory in the past, e.g., wholly SFQ memory in Japan [55, 56, 57], hybrid SFQ-CMOS in the USA [58] and JJ-MRAM, which is under development now [59, 60, 61]. However, these approaches are not suitable for the local storage units. Local storage units need to be designed in a new way to satisfy the requirements of frequency, latency and energy-efficiency.

This chapter first reviews the three memory approaches in superconducting memory design, then discusses the opportunities of designing local storage units with RQL. Finally, the research goal will be provided.

### 3.1.1 Wholly SFQ memory

In 1999, a Japanese research group developed a 16 Kbit superconducting latching/SFQ hybrid (SLASH) RAM with the frequency of up to 10 GHz. In this RAM, the decoders are composed of DC powered SFQ circuit, while the drivers and sense circuits have to be composed of AC powered latching devices. This RAM is demonstrated at low frequency, but fail at a high frequency of around 10 GHz because of the high-frequency AC powering [55, 56].

The next generation of the RAM is a RSFQ pipelined RAM. This is an all-DC-powered RAM with the capacity of 64 kbit - 1 Mbit. This RAM operates at 10 GHz and the maximum power dissipation is 12 mW for a 1 Mbit version.

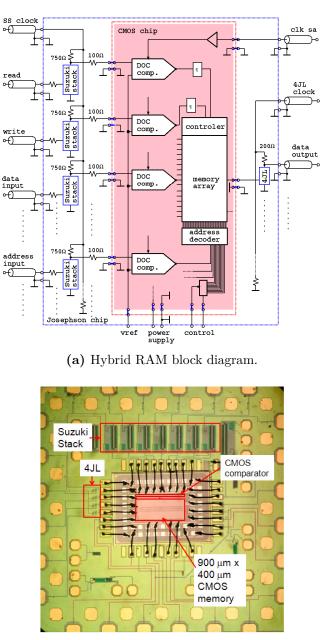

### 3.1.2 Hybrid Josephson-CMOS Memory

Hybrid memory is another approach to large capacity memory in superconductor technology by combining a room-temperature CMOS memory and a RSFQ interface circuit. A hybrid Josephson-CMOS memory was implemented in 2012 [58]. A 64 Kbit CMOS static random access memory (SRAM) is used as the storage component. In the hybrid interface circuit, a Suzuki stack (SS) with a four-junction logic (4JL) is used to amplify the millivolt superconductor logic signal and drives a sensitive CMOS comparator to produce volt level signals for CMOS circuit, as shown in Figure 3.1 on page 33.

The Josephson chip is fabricated using Hypres 4.5 kA/cm<sup>2</sup> niobium technology on a 5 mm  $\times$  5 mm die. The CMOS SRAM is fabricated using TSMC 65 nm technology on a 2.0 mm  $\times$  1.5 mm chip. These chips are connected by short wirebonds in a piggy-back package [58]. The access time is 400 ps and the power of read operation is 12 mW.

The latency and the energy efficiency of the hybrid memory are relatively high. And the major energy consumption comes from the interface circuit. As the result, hybrid memory is not a good approach to on-chip storage that requires low latency and high energy-efficiency.

(b) Hybrid RAM microphotograph.

Figure 3.1: Hybrid Josephson-CMOS RAM [58]. © 2013 IEEE.

### 3.1.3 JJ-MRAM

Unfortunately, the two approaches discussed above have high energy consumption when costs of cryocooling are taken into account. To address this and

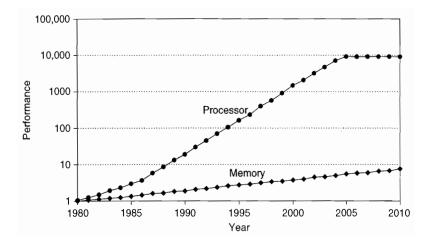

Figure 3.2: The performance gap between processor and memory [62].

other issues, a new type of cryogenic memory, energy-efficient high-density non-volatile JJ-MRAM, is under development [59, 60, 61]. This memory is built with magnetic Josephson junctions (MJJs). A MJJ is a JJ integrated with a ferromagnetic layer. Two distinctive states with high and low critical currents are provided in a MJJ, representing logical '0' and '1', respectively. This MJJ-based approach is electrically and physically compatible with SFQ circuits, allowing the fabrication of memories and processing units in the same chip.

## 3.2 New Opportunities in Energy-Efficient Local Storage Units Design with RQL